Tool/software:

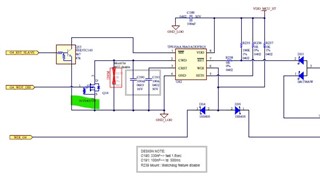

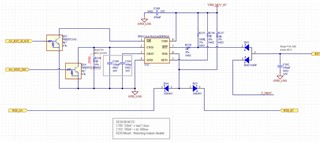

Once designed the above circuit schematic, I'm now testing it. The issues I'm encounteirng are:

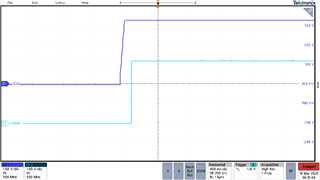

1) Leaving Q14 open (not driven, so Watchdog enable), with SET0=1 (as in the schematic), the RESET out pin is not asserted, regardless of the Twd (watchdog time).

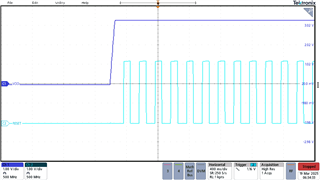

2) Leaving Q14 open (not driven, so Watchdog enable), with SET0=0 , the RESET out pin is asserted after about 3.8sec time, even it the setting should be 1.6sec ( 4,95e+6 * Cwd , with Cwd=330nF)

3) Leaving Q14 open (not driven, so Watchdog enable), with SET0=0 , and lowering Cwd to 100nF (from original 330nF), the RESET out pin is asserted after about 1.8sec instead of time, even it the setting should be about 0.5sec). In that case the watchdog disable feature drving Q14 does not work.

According to the note reported on datasheet par 8.3.2.2 "Pinout options A, B offer watchdog timer control using a capacitance connected between CWD and GND pin. A capacitance value higher than recommended or connect to GND leads to watchdog functionality getting disabled", how do I disable the watchdog and set the proper WDT time?

thanks