Tool/software:

Hello Team

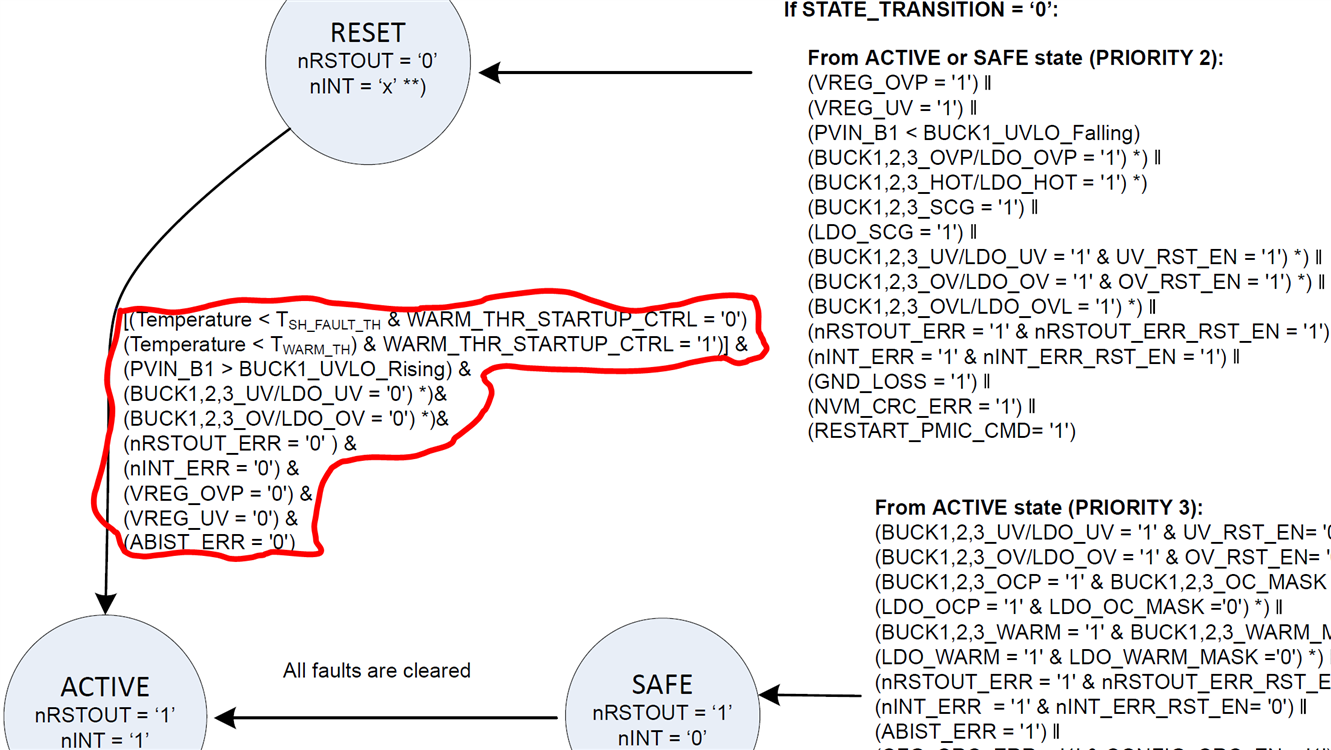

we are using TPS650332-Q1 PMIC

I would like to know how to come out of reset state

For Priority 2, the PMIC can go either Reset / WT_PWR_REC,

"" In order to exit the WT_PWR_REC State, the voltage on VSYS and VSYS_S must go below the VSYSUVLO_THRESHOLD so that the device can enter the OFF State"""

So how to exit of Reset state ?

Please let me know