Tool/software:

Hello,

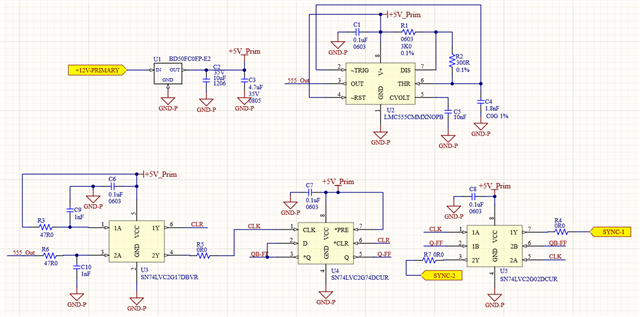

I am designing a 4-phase interleaved PFC. I have designed the 2-phase version of it. In the 2-phase version, I have used the internal Oscillator. In the 4-phase version, I have to use 180 degree phase shifted external Sync signals. I have designed a 555-timer and D Flipflop based circuit to generate the signals. Can you please review the attached circuit and see if I can use it to generate the sync signals ? Please recommend any changes if the circuit has issues.

Thanks.