Tool/software:

Hi team,

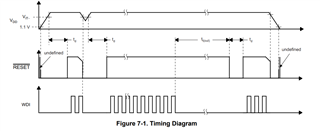

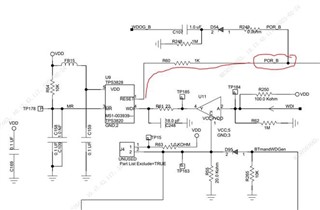

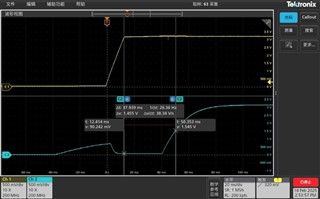

Customer design is shown as below. test point is at POR_B ( red circle). During VDD power up, RESET will have a glitch. Yellow waveform is 3.3V VDD. Blue waveform is the waveform on POR_B ( RESET pin). I was wondering why there is a glitch and how to eliminate it. Thanks!

Rayna