Tool/software:

Hi Team,

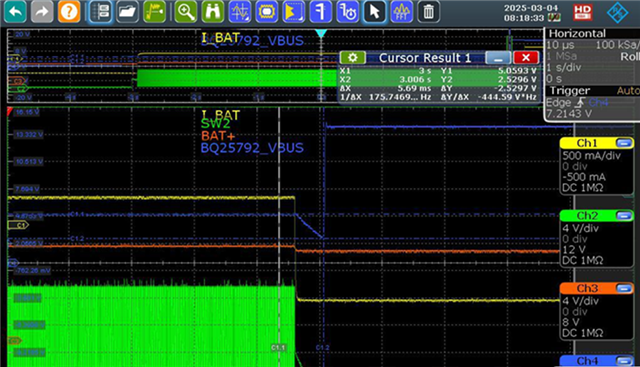

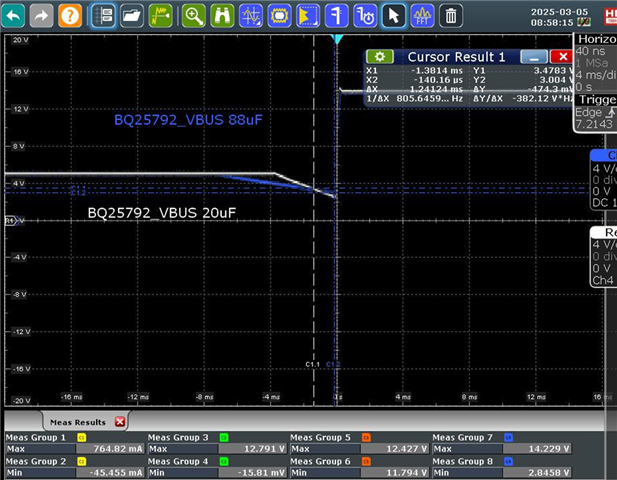

We met the noise issue operating in PFM mode.

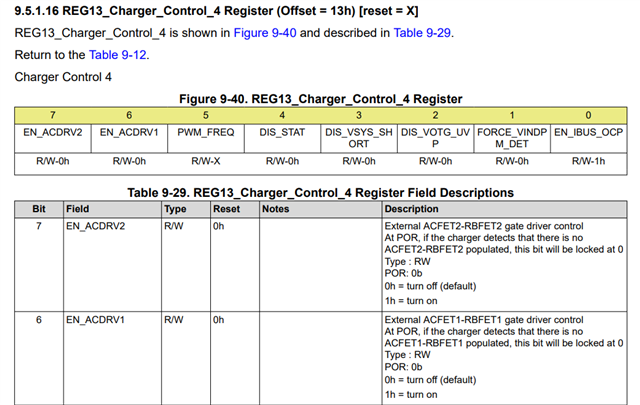

And we tried to use the bit to let BQ part operate in FPWM mode. (PFM_FWD_DIS) And it could work. But when we do the VAC1/2 switch over, the bit may be reset to enable PFM. Does it make sense to you?

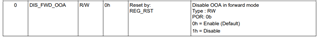

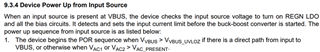

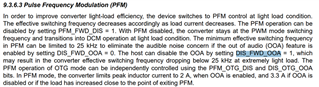

In addition, I found below content in datasheet. Do we need to set both of DIS_FWD_OOA and PFM_FWD_DIS to reduce the PFM noise?

Regards,

Roy