Tool/software:

Hi team,

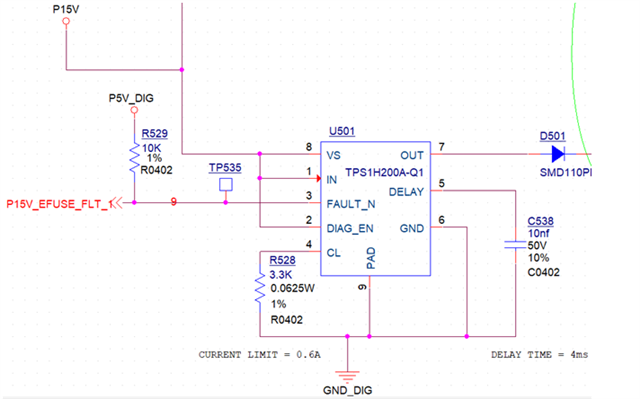

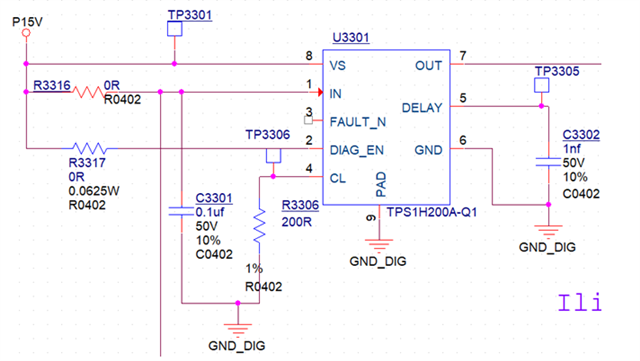

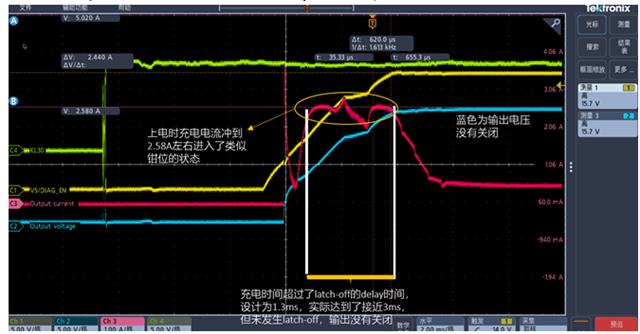

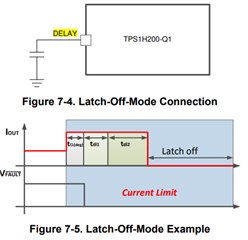

When we applied the TPS1H200A-Q1 high-side switch chip, we encountered the problem of triggering latch-off when powered on. We need to confirm with you:

1. The logic of fault diagnosis when powered on?

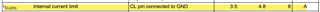

2. When we tried to set the current limit to 10A, we found that it could not be reached. The actual maximum was less than 3A. So I would like to ask, what is the maximum value of the current limit threshold that can be set?

3. I also want to confirm the timing method after the current reaches the current limit. If the current drops below the current limit halfway and then reaches the current limit again, will the timing be restarted?

Thank you for your support!

BR,

Ethan