Tool/software:

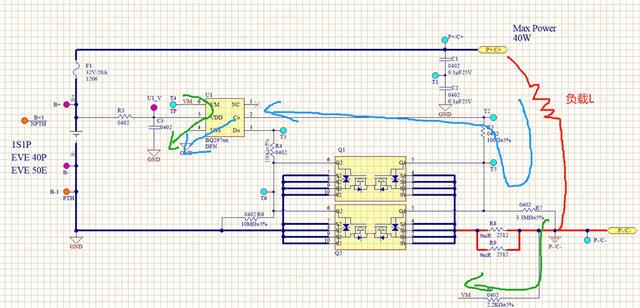

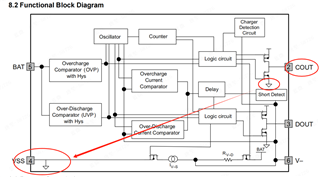

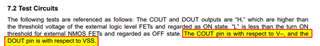

The customer is concerned that there will be leakage current in the below two circuit loop under over current protection and under voltage protection.

Could you help to comment on this?

Blue one (B+)P+--Load--P negative--R7--R5--CO--VSS--B-

Green P+--Load--P Negative--VM--VSS--B-?