Other Parts Discussed in Thread: LM5123EVM-BST

Tool/software:

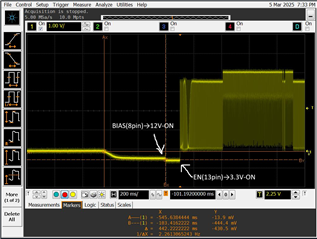

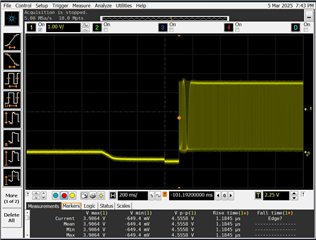

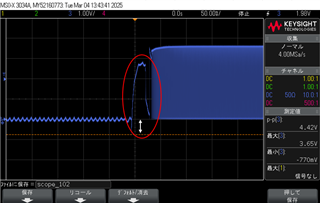

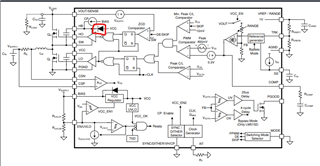

Hello I need an answer urgently. I am designing a boost converter circuit (Vin 7-32V, Vout 15-43V) using LM5123.

In the circuit I designed, burnout has occurred at pin 7 (HB terminal) in a specific location or in the test environment.

Could you tell me what could be the cause of this?