Tool/software:

Hi,

The absolute maximum ratings list a relaxed specification of <20ns.

Is this because the LM5148's deadtime is 20ns (typ.)?

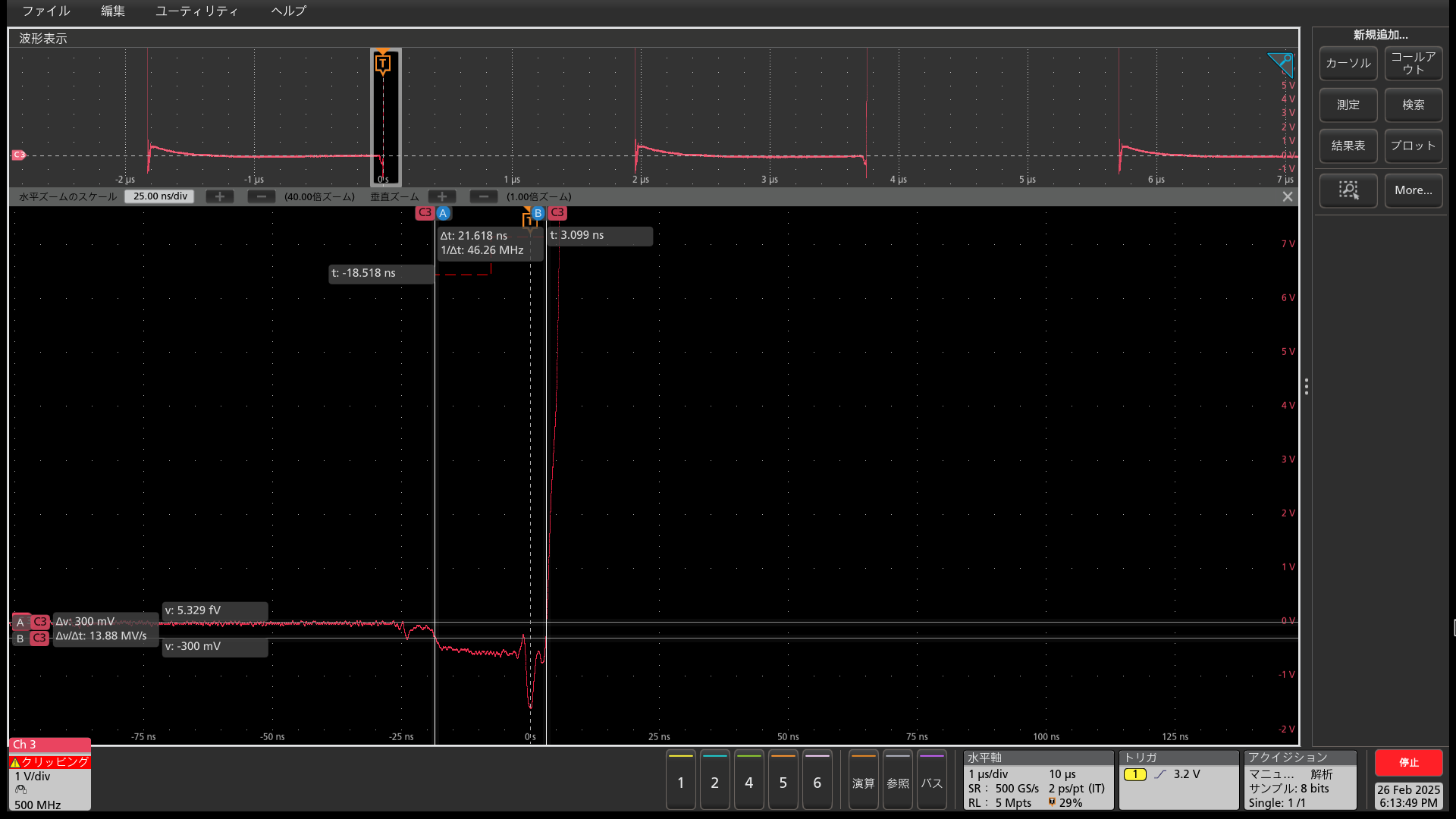

The figure below shows the waveform at the SW terminal.

The time it falls below -0.3V is more than 20ns, so it does not meet the absolute maximum rating.

I think this is because it was evaluated using an individual with a deadtime of around 22ns, but can we assume that there is no problem if it exceeds 20ns slightly?

Best regards,