Other Parts Discussed in Thread: TINA-TI

Tool/software:

Hi E2E Elites,

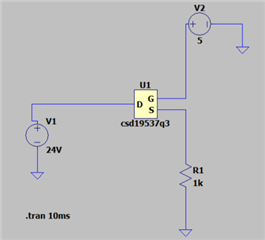

I'm currently using the spice model downloaded from TI website and created a symbol inside LTSpice.

Based on the datasheet it says, Vgs needed typical 3V so that my 24V able to drop on my R1.

Below is my simulation result:

The results shown at source side is only 2V instead of 24V.

Am I miss out anything?

Thanks.

Regards,

JS