Tool/software:

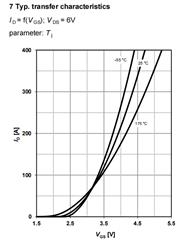

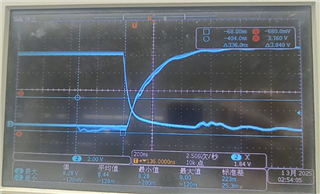

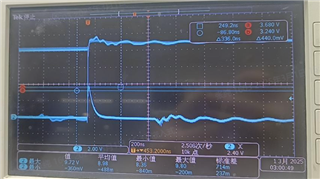

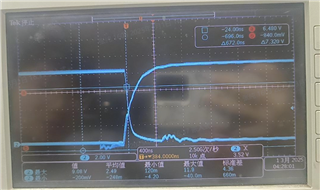

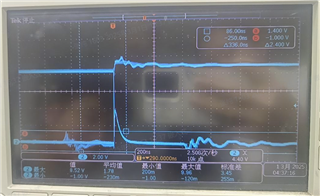

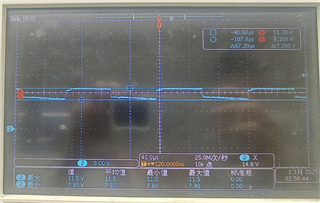

Hello expert, I encountered an issue of HS pin burnout while using UCC27282 for BLDC applications

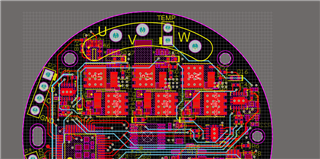

1、This is the schematic diagram I am using

2、The motor is applied to scenarios with fast response and high load, and can instantly respond to high loads. When using a switch power supply (48V) for power supply, everything works normally; But when using a battery pack (fully charged at around 58V), the HS will burn out at the moment the motor starts, aand the accompanying MOS transistor may also break.

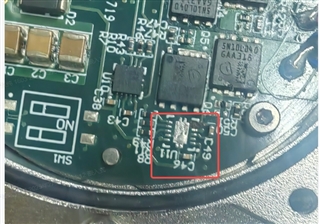

3、This is a burnt board

Looking forward to your reply very much