Other Parts Discussed in Thread: UCC3818

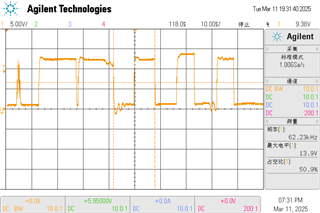

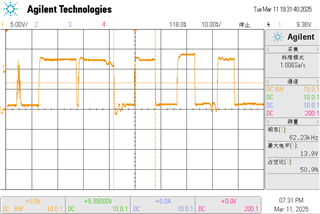

Tool/software:

Hi

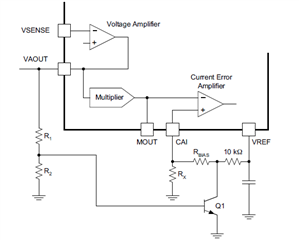

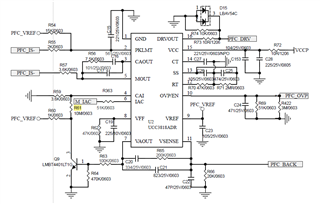

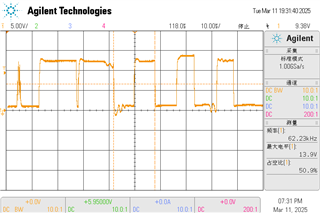

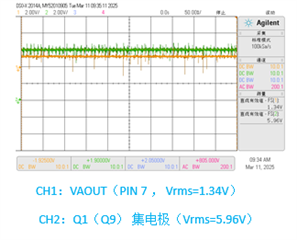

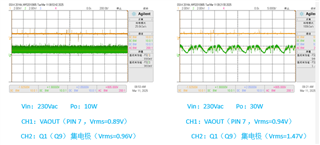

For last UCC3818A noise issue, this problem is still. and now we want to check the CAI pin. and we read application note slua309c. but we don't know how to caculate the Rbias in slua309c as below picture 1. also the R61 (highlight as orange) in picture 2 ( customer schematic) . Could you help tell us how to caculate it ? or provide relate caculate file. It's best if you can help caculate it. thanks.