Other Parts Discussed in Thread: UCC28810,

Tool/software:

Hello,

I am referring the design document for the 48W ceiling fan (), which uses UCC28810. The internal block diagram for both the ICs is the same.

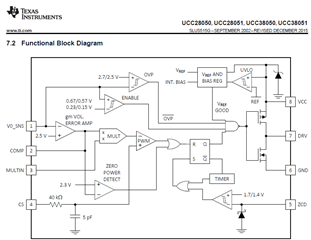

UCC28051 internal block diagram:

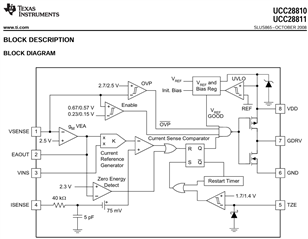

UCC28810 internal block diagram:

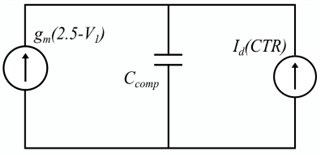

For the application note attached, where UCC28810 IC is used in a flyback topology with output voltage sensed through an auxiliary winding and opto-coupler, fed to pin 1 and pin 2, respectively. How does the zero power detect block (connected to the comp pin IC) get activated during output light load/no-load conditions?

P.S.: I know the pin 3 voltage has to drop below the comparator ref voltage (2.3V for the zero power detect case). What I am asking is, during light loading, how is that voltage with the below circuitry reflected on the pin 3 cap?

48W Ceiling Fan TI ref design.pdf

Thanks,

Shivam Chakraborty