Tool/software:

hi there,

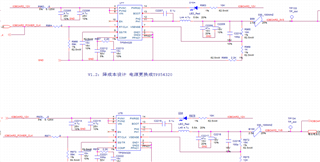

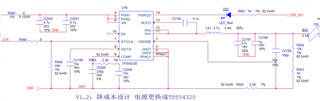

we have 3 TPS54320 on board. sch as below. FPGA IO provides external clock to drive both three power IC. 800khz

At the beginning, FPGA output external clock as as HIGH signal, we hope the IC works by RT resistor. however, at this time, the PH waveform is about 60khz, and the output ripple is large as 1Vpp. this is abnormal.

then FPGA output 800KHZ 50% duty cycle external clock, and after 50ms, the PH waveform is ok 800khz.

And evern very strange, this problem happens occasionally when the temperature is -20°C on different boards. we can repeat this phenomena by use freezer spray on TPS54320.

We noticed that 3 RT resistor are actually in parallel, so the equivalent RT resistor is 59K/3. but we can not understand how the 60khz PH come from. Questions:

1, could you pls provide the internal structure of RT/CLk pin inside thee IC?

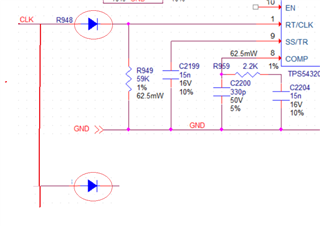

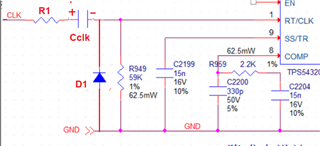

2, we tried change the 0 ohm on external clock (R948, etc) to a Capacitor, and things become normal when ac coupled. We do not want to insert 3 independent buffer (PCB revision), can we use like this? there is no relevant info in datasheet.

any other advice is welcome, especially about the low temperature.