Other Parts Discussed in Thread: TPS65987D, TPS65987

Tool/software:

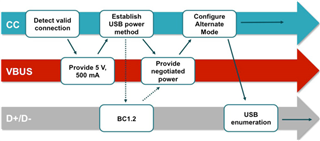

On the TUSB1046EVM, during the DP alt-mode configuration sequence is the USB enumeration done by the TPS65987D D+/D- pins 50/53? We plan on connecting our ULPI PHY D+/D- to the same USB Type-C pins. Can we transmit and receive data from our ULPI PHY D+/D- after the TPS65987D is done with DP alt-mode USB enumeration while the GPU is transmitting video through the TUSB1046? We'd like to have USB2.0 data communication regardless of whether the TUSB1046 is in USB3.1+2 lane DP or 4 lane DP mode.