Other Parts Discussed in Thread: TPD1E01B04

Tool/software:

Hello Team,

Please help to review the schematic of HD3SS3220IRNHR section as per the attached document.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello Team,

Please help to review the schematic of HD3SS3220IRNHR section as per the attached document.

Hi Yasar,

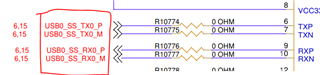

I cant see where these pins go:

The control pins looks ok, but I cannot see where some of them are connected.

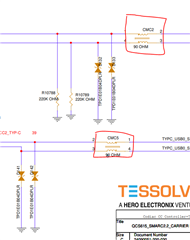

For the connector side high speed traces:

make sure the CMC bandwidth is sufficient for datarate desired

The Clamping voltage of the ESD may be too high. Aim for a value closer to 5V

Hi Vishesh,

Thanks for the quick feedback.

Please see the replies in-line

I cant see where these pins go:

[MSY]_These are mapped to SoC's USB controller port.

The control pins looks ok, but I cannot see where some of them are connected.

[MSY]_below is the control signal implementation for HD3SS3220.

Hope this works well for DRP mode?

| HD3SS3220 control pins | Implementation | Remarks |

| INT_N/OUT3 | Mapped to SoC's GPIO via 5V to 1.8V level shifter | As an Interrupt pin to SoC |

| ID | Mapped to SoC's GPIO via 5V to 1.8V level shifter | To control HOST/Device Mode via SoC |

| SCL/OUT2 | Mapped to SoC's I2C port (1.8V level) | |

| SDA/OUT1 | Mapped to SoC's I2C port (1.8V level) | |

| VCONN_FAULT_N | Given PU to 5V rail. Not mapped to anywhere else. | |

| CURRENT_MODE | Given PU to 5V rail. Not mapped to anywhere else. | |

| ADDR | Strapping option given with default PD |

make sure the CMC bandwidth is sufficient for datarate desired

[MSY]_Do you have any recommendation here?

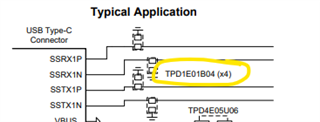

The Clamping voltage of the ESD may be too high. Aim for a value closer to 5V

[MSY]_Datasheet of TPD1E01B04 says, this is applicable to USB-C ESD protection.

Do you still think that, need to change this?

Hi Yasar,

Yes the pin strap config should be ok for DRP mode. Make sure PORT pin is left NC for DRP mode.

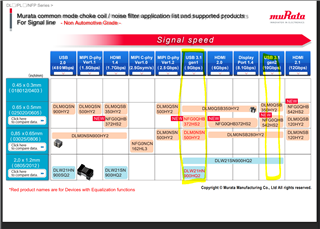

For CMC I use the following parts as a recommendation:

For ESD, we recommend a lower clamping voltage as this has a better impact with TI parts. I recommend using the PUSB3FR4.