Other Parts Discussed in Thread: SN6501,

Tool/software:

Hello,

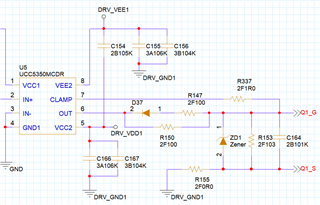

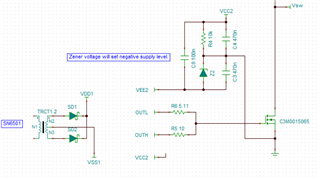

I have designed a gate drive circuit utilizing the UCC5350M.

Would there be any issues with applying a negative voltage to the VEE2 pin?

I would appreciate any technical advice or feedback on the circuit design.

The circuit is designed for use with a SiC FET.

VCC2: 18Vdc

VEE2: -3Vdc

I would be grateful for any insights or recommendations.

Best regards,