Tool/software:

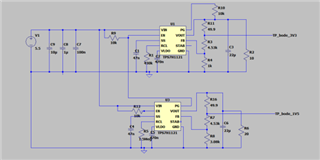

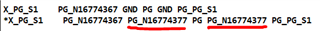

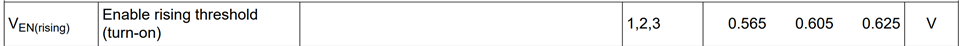

I'm trying to simulate a sequence of 1.5V (1V5) in LTspice, where the PGOOD (PG) signal is supposed to enable 3.3V (3V3) once FB reaches 90% of the reference voltage.

However, PG does not seem to function correctly—it looks like the NMOS tied to PG is always closed instead of waiting for FB to cross the 90% threshold.

Here’s what I expect:

- PGOOD should be low (0V) at startup, keeping the NMOS closed.

- Once FB > 90% of VREF, PG should transition high, opening the NMOS and enabling pull-up Voltage

Instead, in my simulation, PGOOD follows an unexpected behavior, and the NMOS seems closed all the time, not waiting for FB to reach the threshold.

Any insights into what could be wrong? Could this be a modeling issue with E_PG_ABM9 or the NMOS switch definition?

Thanks in advance!