Other Parts Discussed in Thread: TPS7H4010-SEP

Tool/software:

HI,

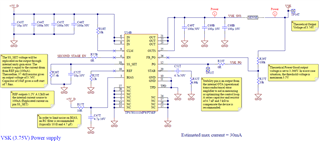

I want to generate a voltage of 3.75V using the LDO TPS7H1111MPWPTSEP. For that purpose, I implemented the following circuit.

The 5V input are coming from a DC/DC the TPS7H4010-SEP whose switching frequeny is set to 350kHz.

To set the output voltage to the desired level, I connected a Rref=12k to the REF pin and Rset= 37,4k to the SS_REF pin. The Css added in parallel with RSET allows a better stability and a lower output noise and set the soft start time to 7.8ms.

The CLM (current limit mode) is connected to Vin for brick-wall current limit mode.

Rfbpg_top= 100k and Rfbpg_bot = 10k so that the theoretical threshold output is set to 3.366V.

A capacitor (CCOMP) and resistor (RCOMP) of 4.7 nF and 5 kΩ recommended are placed in series to the STAB pin to compensate the device.

The Css at the soft-start pin as been replaced by two 10uF in parallel to set the soft start time to ~34ms.

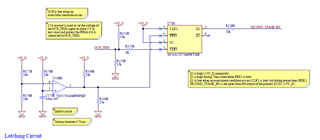

The VSK is enabled by the output of a Latching circuit (powered with the 5V), which during start up is inhibited to that its output follow the ramp up of the 5V.

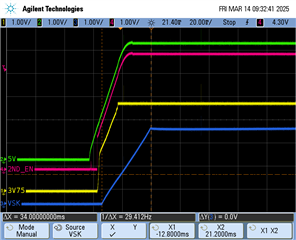

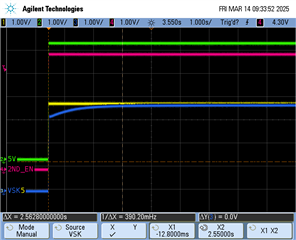

At start up we observed the following behavior (the 3V75 trace is not relevant here, we are interrested in VSK):

VSK which is the output of the LDO ramps up to 3.25V in ~34ms than only reach slowly 3.75V is ~2.5s.

Do you have any idea why VSK would not ramp up directely to 3.75V in ~35ms?

Thank you in advance for you help