Other Parts Discussed in Thread: PMLKBOOSTEVM,

Tool/software:

Hi

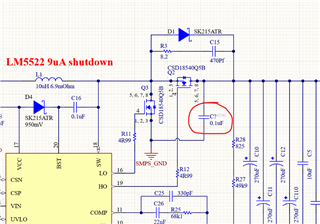

I've used Ti webench to design a SMPS with the LM5122.

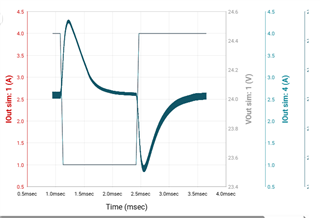

Specs : Battery suply - 8-16 VDC Output 24vdc - 4 AMPS - 30 Celcius ambiant

This is not very exotic, but this is what I need to do for this project.

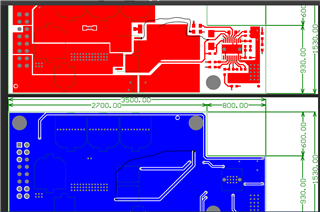

TI webench show 50mV of noise peak to peak, I did try to respect the routing note and the proposed general placement.

I'm aware that the noise can be quite different in real life vs Webench, and I am a 20 year + digital designer , but I would like an active engineer at TI to review my design.

Looks to me that a few components may be missing from this webench design.

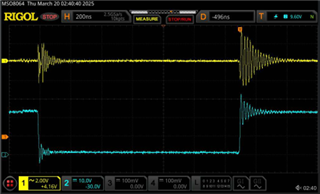

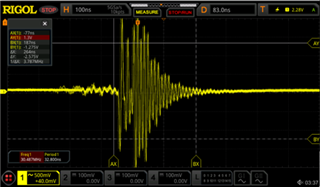

Noise on bare design is more than 3V pk-pk.

Adding a 100uF cap at the output lower that to 1V pk-pk but it is still very High. Adding more doesnt have as much effect.

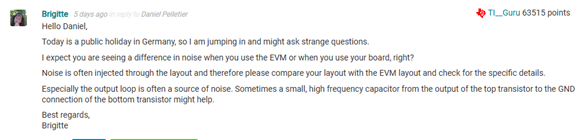

Ive seen in the forum that a few person did implement the same design, and they were told to add 100ohms and 100pF on the current feedback resistor. It was quite a challenge to implement, but I did.

We didnt see any change at all.

I dont want to restart this part of the design from scratch with another part or another brand at this point, I would prefer having someone from the power management to look at it.

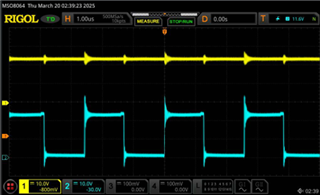

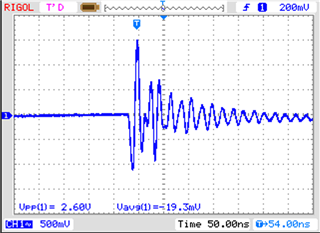

waveform from webench

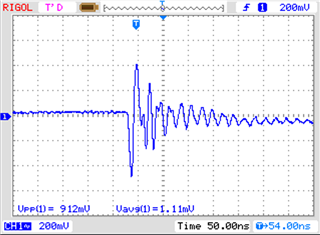

Actual circuit with a 24V out 8ohms load (3 amps)

Thanks

Daniel Pelletier