Tool/software:

Hi TI team,

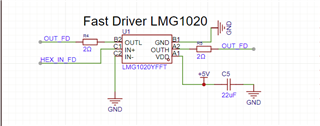

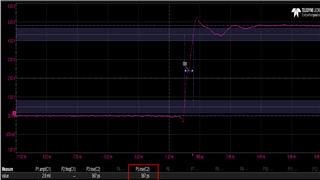

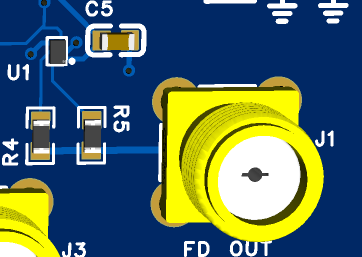

I am using the LMG1020 as a fast rise time driver, and I have attached my schematics and oscilloscope screenshots for reference. The screenshots show a measured rise time with a scope that can measure less than 300 ps.

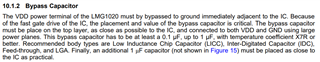

However, I noticed that the rising edge is not perfectly sharp—there is a noticeable bend in the rising edge, which is not present in the datasheet examples. Could you help me understand why this behavior is occurring? What could be the possible reasons for this deviation? Additionally, if you have any suggestions on improving my circuit to achieve a smoother and faster rise time, similar to the datasheet specifications, I would appreciate your guidance.

Also, if you have an IC that provides an even faster rise time than the LMG1020, please let me know.

Thanks!