Tool/software:

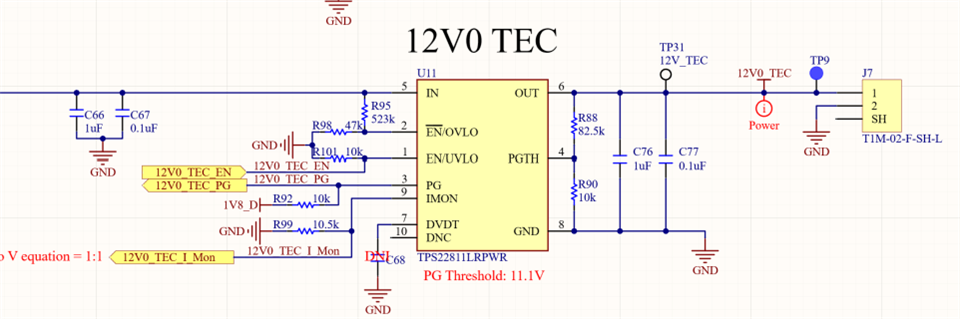

I have implemented the following design using TPS22811LRPWR but am unable to enable the 12V0_TEC output. The way I have it configured, I have a resistor divider to set the nEN/OVLO. With the 12V input that puts appx 0.9V on this pin. However, instead of continuing the resistor divider I have connected the EN/UVLO pin to a CPLD at 3.3V logic level. This way we can enable and disable the 12V0_TEC as we see fit via the CPLD pin. At startup, the voltage on this pin is 0V until the CPLD writes a logic high (3.3V) at which point I would think both the UVLO and OVLO conditions are met and the device should turn on. However, when we write 3.3V to this pin, the device will not turn on. Is this not an acceptable way to implement this? Do you see any other issue with this schematic that would prevent the device from turning on?