Tool/software:

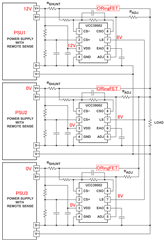

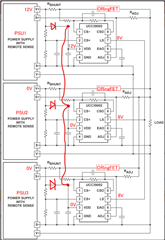

The configuration is to operate three PSUs in parallel, with each output connected via an ORingFET.

PSU1 may have an output voltage of 12V, while PSU2 and PSU3 may have an output voltage of 0V.

The LS pin is common to each UCC29002DR/1 and VLS = 8V.

PSU2 and PSU3 have VDD = 0V.

The absolute maximum rating for the LS pin of the UCC29002DR/1 is VLS = -0.3V to VDD. Is there any problem with using it this way?