Tool/software:

We are using TPS3808G01 for our new project design.

Our architecture is:

- Our Sense signal, we keep it in safe zone, ya. (First power-up, and > 0.405V)

We have some questions:

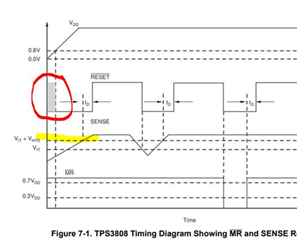

- VDD < 0.8V, is undefined state, right?

- When VDD ramp up from 0.8V to 3.3V, Reset pin, will it driving low, possible?

- VDD < 1.65V, then Reset pin, for sure low state, is it?

We need to clarify these points, thanks.