Other Parts Discussed in Thread: UCC28C43

Tool/software:

Hello Team,

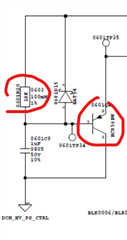

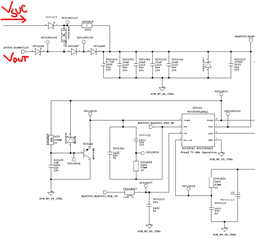

I'm using the UCC28C43 as the flyback controller (DCM operation). I have designed a startup circuit to supply the controller intially. This will supply until the flyback output is ready to takeover the controller consumption. At slow ramp up of flyback input voltage, the Startup Circuit (SUC) will supply the energy and increases the Vdd of the controller. When Vdd reaches the ON threshold the controller draws some energy from the Vdd capacitors to generate Vref and after some time the PWM. The PWM duty will gradually increase to its full value when the soft start time is completed. Now my question is related to the energy required by the controller during this soft start phase of the controller.

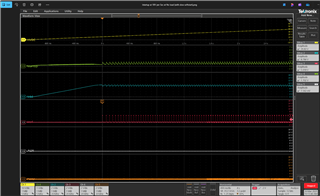

In my application, the soft start time is chosen as 180ms (replaced 1uF CSS cap with 10uF for these measurements). When the input voltage of flyback ramp up is faster (80V/s), the energy coming into the Vdd capacitors is sufficient to deliver the controller requirement. Hence the PWM are generated and the flyback can take over the consumption of controller and bypassing the SUC.

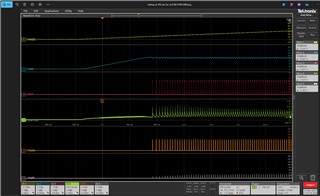

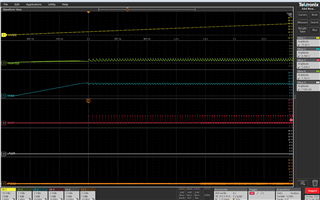

But when the flyback input voltage ramp up is slower (10V/s), there are no PWM generated. Beacuse some events are happening in the controller which need energy from the Vdd capacitors and this drops the Vdd below the Turn OFF threshold of the controller and turns OFF the controller. This is kind of a hiccup mode and continous as shown in the below image.

Could you please explain the following queries in this context:

1. What happens inside the controller after VREF is generated and before PWM pulses are generated?

2. How much current does the controller need during this phase of operation?

3. Does increasing or decreasing the soft start time will influence the amount of energy required by the controller? If YES how will it influence?

Awaiting your quick answer!! Thanks in advance!!

Chaitanya K