Other Parts Discussed in Thread: TINA-TI

Tool/software:

Hi Team,

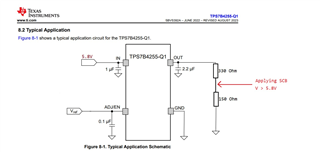

I have TPS7B4255QDYBRQ1 in my design. The condition for Reverse current protection is given as Vout > Vin. My Application is given below.

Here an SCB is applied at the voltage divider. But the voltage at Vout of Tracker may not rise to SCB voltage. This can cause a reverse current flow.

Given that the datasheet mentions a maximum reverse current (IREV) of 0.25 µA, I would like to understand how the tracker device will respond to this condition. Specifically, will the reverse current still be limited to the maximum IREV mentioned in the datasheet, or should I expect a higher reverse current due to the condition not being met?