Tool/software:

Hello

We have included the TSP26633 in a design.

During our initial board bring-up, we have tried to perform over-current tests on the board to verify that the TPS26633 shuts down the current to the rest of the circuit.

Unfortunately, the TPS26633 overheats very quickly as soon as the current limit is exceeded and catches fire within a few seconds. This has now been seen on 2 separate boards.

The load current at which the ICs were burned up was 4.6A, i.e. on 100mA above the current limit threshold.

The load used during testing was an electronic load set to 4.5A. 4.5A was tested for several minutes with a thermal camera, the temperature was at no point over 40°C.

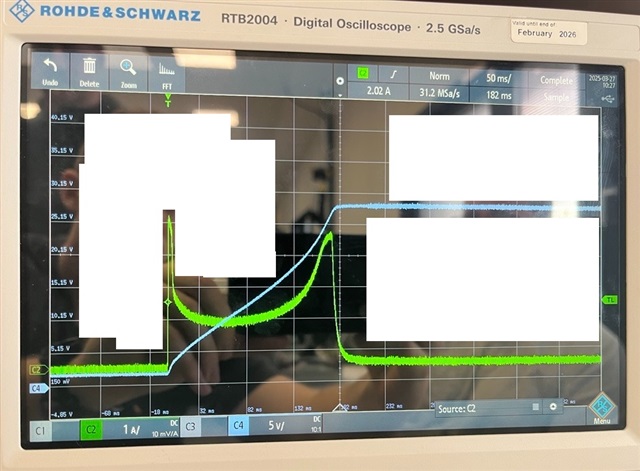

Next test was to increae the load to 4.6A to very shutdown. Shutdown did happen, but during auto-retry the IC started burning.

The load capacitance during test was 12mF. The inrush current was also measured at startup (SHDN de-asserted) and this matches very closely Figure 8-4 in the TPS2663 datasheet with an initial peak value of 4.5A

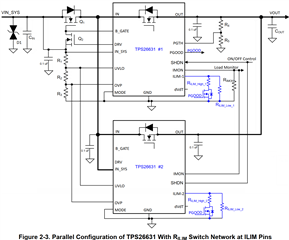

The schematic is shown here:

Please advise as to why this can happen?