Tool/software:

Hi team,

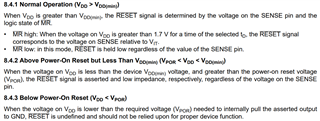

My customer has a design with TPS3808G1, and the sequence is SENSE first (> VIT + VHYS), and then VDD (3.3V) goes up. Engineers need to know the SENSE state when the VDD transient period goes from 0.8V to 1.7V. Could you help answer this? Thank you!

From the datasheet, the recommended operating minimum VDD is 1.7V and the SENSE state is undefined when VDD < 0.8V.

Regards,

Sam Ting