Tool/software:

Dear support team,

On our custom pcb board are four TPS274C65 chips connected to the same SPI bus. Two chips are using their internal voltage regulator where the VS input is supplied by +24V and protected by an eFuse. The other two chips are supplied by an external +3V3 voltage regulator through their VDD pins. Their VS inputs are also supplied by +24V and protected by an eFuse.

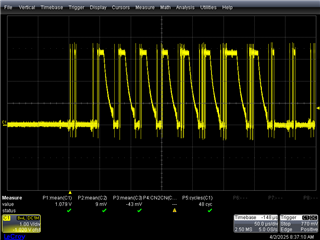

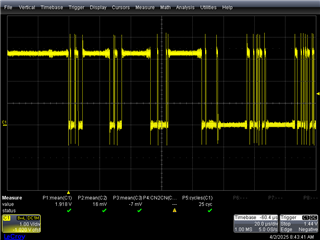

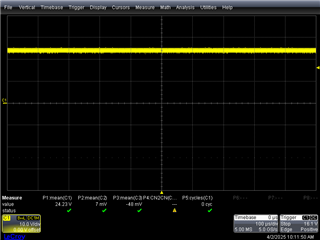

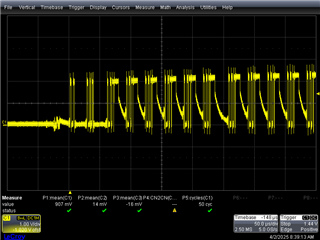

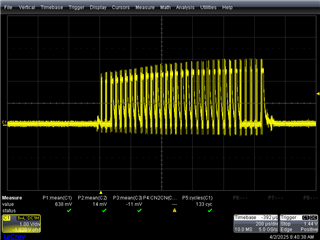

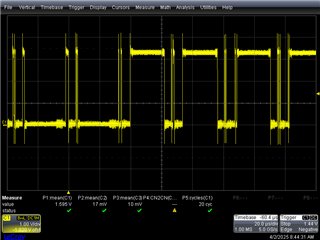

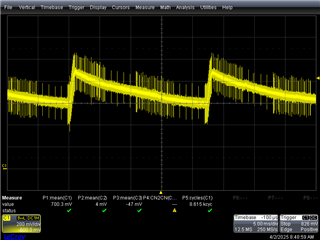

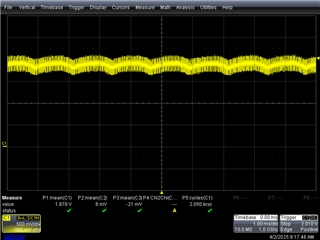

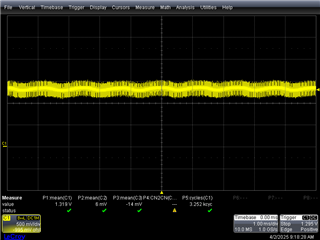

The SPI communication between the microcontroller and the TPS274C65 chips works correctly when all four chips are powered. If a TPS274C65 chip with internal voltage regulator has no VS supply, it will affect all other active TPS274C65 chips on the same SPI line so that they won’t work correctly. This unsupplied chip will probably pull down the data signal of the MISO line. In this case, a high-level signal transmitted by an active TPS274C65 chip won’t exceed the high-level voltage threshold of the microcontroller and therefore won’t be validated correctly.

If the two TPS274C65 chips aren't supplied with power, there will be a voltage drop on the MISO line of at least 300 mV compared to the signal where all four chips are supplied with power.

This voltage drop dpends on the amount of the data traffic on the MOSI line. With a small amout the high level is around +2V and with a large amout around +3V.

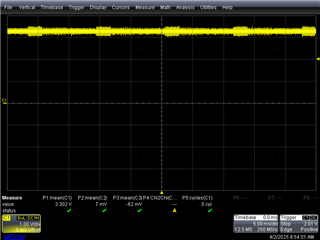

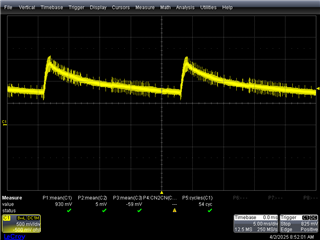

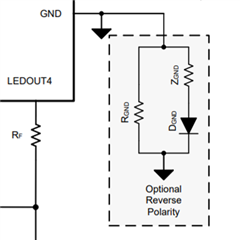

The measurement of the voltage signal at the VDD pin of an unpowered TPS274C65 chip shows a capacitive charge and discharge signal up to +2V with a frequency period, that corresponds to the SPI communication poll time.

Is this a desired/known behaviour of the TPS274C65 chip?

What solution is recommended to avoid this behavior?

Thanks in advance.

Regards,

Aron