Tool/software:

Hi Team,

Would you please share the light load operation mode with me? I can NOT find the light load operation conditions/mode introduction at datasheet.

Are this PFC/PWM controller support burst mode?

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Team,

Would you please share the light load operation mode with me? I can NOT find the light load operation conditions/mode introduction at datasheet.

Are this PFC/PWM controller support burst mode?

Thank you.

Hi Ning,

I notice that PFC stage was turned off by UCC28512 due to trigger the zero-power detection feature. Moreover different PSUs has different threshold since the Zero power comparator threshold tolerance is quite large. (Min. 0.2V, Typ. 0.33V, Max. 0.5V).

Is there any methods can avoid IC into zero-power detection?

Is this feature can be disable?

Is adjusting VAOUT compensation network can slow down the VAOUT voltage below threshold?

Thank you!

Hello Muhsiu,

The zero-power comparator function cannot be disabled. Its purpose is to ensure that the gate-drive output GT1 is shut off in the event that the VAOUT votlage is driven low by rising output voltage.

Even though a similar function seems to exist in the MOUT output equation (factor of (VAOUT-1)), this device uses Leading-Edge-Modulation in the PFC section which drive high duty-cycle PWM pulses when MOUT = 0. The Zero Power function will block those.

Adjusting the VAOUT compensation may slow the voltage drop below the threshold but will not stop it, so there is no point to having an extremely slow voltage-loop response.

To avoid the zero-power condition, you may have to add a small minimum load to the PFC output so that there literally is no zero-power condition.

It would need just enough load to keep VAOUT above the 0.5V maximum Z-P threshold.

Adding a small positive offset voltage (5~10mV) to the ISENSE input may also help.

Regards,

Ulrich

Hi Ulrich,

Thanks for your feedback!

Due to the AC input current fluctuations was observed from of the shelf PSU, it might not easier to add minimum load to the PFC output.

The additional load generate heat and reduce energy efficiency.

My goal is minimize the components change.

Regarding add a positive offset voltage to the ISENSE pin, Would you please share more details?

From the block diagram view, the Zero power comparator is independence(or isolation) from the voltage and current compensation network.

Thanks again.

Muhsiu

Hello Mushiu,

The Zero-Power comparator is not independent, it is directly connected to the VAOUT signal which is the output of the voltage-loop compensation network.

For the ISENSE offset voltage, connect a high-value resistor (Roffset) from VREF (pin20) to ISENSE1 (pin16), so that Roffset forms a resistor-divider with the existing resistor from ISENSE1 to GND (refer to R8 in Figure 1, page 11 of the UCC28512 datasheet).

You only need a few mV offset.

Roffset = R8*(VREF-XmV)/XmV, where XmV is the offset voltage you wish to set.

Regards,

Ulrich

Hi Ulrich,

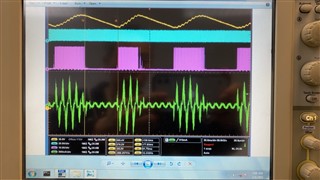

I'd like to double check here, The attached waveform is measured at light load condition. Ch1: PFC output voltage, Ch2: DC/DC PWM, Ch3: PFC PWM, Ch4: AC input current

1. Is above waveform indicating the improperly compensated control loop design?

2. Is that zero-power detection mode a failsafe feature? Or it's the normal operation mode when the PFC output load very light?

3. Is possible to design or optimize the voltage/current compensation network to avoid controller into zero-power detection mode?

4. As you recommended to add the bias voltage at ISENSE1, Is there any side effect?

Thank you again for your feedback.

Muhsiu.

Hello Muhsiu,

1. Yes, I am inclined to believe that the oscillating output voltage seen on Ch1 is caused by an improperly compensated control loop design.

It looks like the loop response is too slow.

I suspect that if you capture the VAOUT signal, it would be above 0.5V when the Ch3 PFC PWM operates and be below 0.5V when there is no PFC PWM.

2. The zero-power detection is intended to prevent an overvoltage on the PFC output due to minimum on-time conditions of the PFC PWM output. If PFC PWM was always active every cycle without any disable, then a finite amount of energy will always be delivered to the output each cycle and Vout will go to overvoltage when there is no PFC load. The zero-power threshold prevents that by detecting when VAOUT is driven below 0.5V and it shuts off the gate drive.

3. It is not possible to avoid zero-power detection if the load is zero-power (Z-P). However, it is possible to optimize the voltage compensation network to speed up the loop response and reduce the time interval between Z-P detections. This will also break up the PFC PWM switching into much narrower intervals much more often, so you will not get such big swells of current as seen on Ch4. And the ripple voltage on PFC Vout will be much lower.

4. The side effect of the offset voltage added to ISENSE1 is to have some dead time in the AC current around the AC voltage zero-crossings.

If there is too much dead time (flat spots where AC current = 0), it will increase THDi and reduce PF.

Regards,

Ulrich

Hi Ulrich,

Thanks for your quick response and suggestion!

The measured loading set as 5% of rating power.

It's not operating at zero-power. However the controller into zero-power detection mode caused by improperly compensated control loop design.

It seems the problem is that the control loop is not properly compensated such that the controller can automatically converge to a stable operating point.

Do you have any spreadsheet or calculation template can shared for compensation network design for studying?

At same time, I will request PSU supplier fine tuning the voltage compensation network to speed up the loop response to see if we can resolve the issue.

Thanks again.

Muhsiu

Hi Muhsiu,

For proper loop compensation design, I suggest to review this application note: https://www.ti.com/lit/pdf/slyt097, at pages 17 and 18.

Several other potentially useful support documents are also available here: https://www.ti.com/product/UCC28512#tech-docs

Regards,

Ulrich