Tool/software:

Hi,

I'm going to use LM5143 to generate single output (10Vin to 3.3V @ 30A). Is this buck controller can be use for single output? If yes, Can you share any reference.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

I'm going to use LM5143 to generate single output (10Vin to 3.3V @ 30A). Is this buck controller can be use for single output? If yes, Can you share any reference.

Hi Roshan

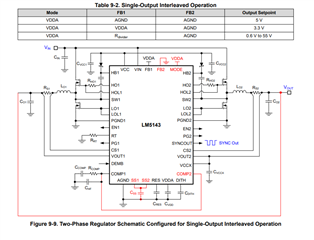

Yes, it can be used for single output. Check following configuration

I would recommend you use LM5143DESIGN-CALC Calculation tool | TI.com for design calculations. It is a very useful tool. Additionally check this reference design - PMP23262 reference design | TI.com

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response & References. I'm planning to use LM5143 not as interleaved configuration. Only as single channel, single output. Is this buck controller can be use for single channel configuration? If yes, Can you share any reference.

Thank you

Regards

Roshan

Hi Roshan

Yes, single channel configuration is possible. Disable ch2 by connecting EN2 to AGND. However, I would recommend using LM5141 for this use case.

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response. If i use the LM5143 as single channel configuration by connecting the CH2 enable pin to AGND. Can i let the unused pin as open?

Thank you & Regards

Roshan

Hi Roshan

EN1/2 should never left open. I would recommend connecting it to AGND.

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response. I designed & produced the module with single channel configuration and let the unused pin as open and EN2 is tied to AGND. The circuit was working fine. My configuration FB1-Buck VDDA. Switching frequency: 400Khz. Buck inductor: 1uH (IHLP6767GZER1R0M01). Current sense type: Inductor DCR (Rcs-7.5K, Ccs0.2uF), Output Cap: 1.8mF, Soft start raise time: 2.3ms

But in startup, BUCK high FET was on for 10us. The IC working sequence was also as first top FET on after that bottom FET on. Also with out switching the bootstrap capacitor was charged to 3.5V (For Circuit reference refer the datasheet circuit). So when the first pulse of High FET on, the output voltage was developed to 2V. I'm enabling the converter at the input 9V. My buck converter output voltage was not match to soft start raise time. Can you clarify the switching sequence of the LM5143

Thanks & Regards

Roshan

Hi Roshan

Could you please share some experimental waveforms of following nodes

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

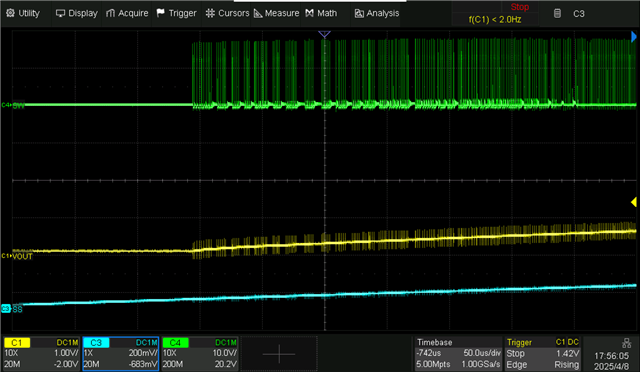

Sorry for late reply, Refer the test wave forms. and provide your feedback

CH1: +10Vin Sw

CH2: Bot FET gate

CH1: 3.3Vout

CH2: +10Vin Sw

CH1: 3.3Vout (Zoomed startup)

CH2: +10Vin Sw (Zoomed First pulse)

CH1: Soft start pin

CH2: 3.3Vout

CH1: Soft start pin (Zoomed startup)

CH2: 3.3Vout (Zoomed startup)

Hello Roshan

SS has inbuilt offset; device will follow SS once it crosses the internal threshold level.

Waveform you shared has two parts

At the start comp voltage goes ahead of its reference and device starts switching, however reference is still 0 V thus device stops switching and gradual fall in output volage can be seen, its minimal as device is operated under noload. Once SS crosses internal threshold, output starts following SS and total startup time is quite closer to what you have designed

I hope these answers your questions. Let me know if need further help

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response. In my understanding, The feedback reference will raise w.r.t soft start voltage. So if ss voltage is 0V. The FB reference will be 0V. So comp voltage also 0V. Also i have another doubt. My switching frequency is 400Khz. So my total time period is 2.5us. But the controller first pulse on time is nearly 12us. I don't know why the controller allow Ton time period beyond its fixed timed period. I tied DEMB pin to VDDA, So my converter operates in FPWM.

Thanks & Regards

Roshan

Hi Roshan

The feedback reference will raise w.r.t soft start voltage. So if ss voltage is 0V. The FB reference will be 0V. So comp voltage also 0V.

- Yeah, that's correct, however it will be true after SS cross internal threshold voltage

Also i have another doubt. My switching frequency is 400Khz. So my total time period is 2.5us. But the controller first pulse on time is nearly 12us. I don't know why the controller allow Ton time period beyond its fixed timed period. I tied DEMB pin to VDDA, So my converter operates in FPWM.

If you look at Zero-cross threshold during startup, it is similar to VDEMB = 0 V, PFM case. Zero crossing is part of the FPWM/PFM logic.

Therefore, you are seeing PFM behavior during startup

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response,

Yeah, that's correct, however it will be true after SS cross internal threshold voltage

I have another doubt, If the feedback reference follows the ss after the ss crosses the internal threshold, how the feedback reference will raise smooth w.r.t ss raise time. Also in datasheet test wave-forms there is no step raise in output.

If you look at Zero-cross threshold during startup, it is similar to VDEMB = 0 V, PFM case. Zero crossing is part of the FPWM/PFM logic.

Therefore, you are seeing PFM behavior during startup

Ok, But in datasheet they didn't mention any huge PFM range. If the controller will operate with this sequence, how to raise the output w.r.t soft start voltage.

Thank you

Regards

Onkar Bhakare

Hi Roshan

Kindly share your schematic for review

Thank you

Regards

Onkar Bhakare

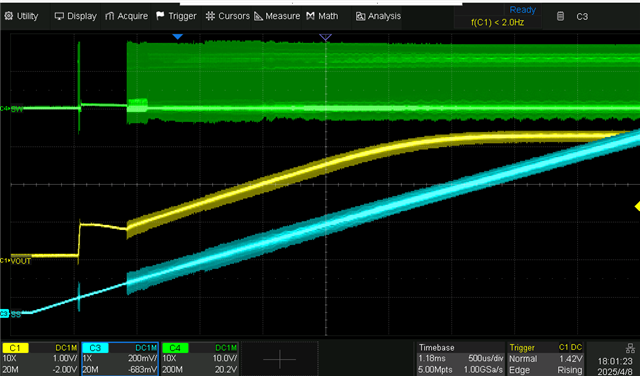

Hi Roshan

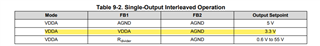

I tested the single output configuration on EVM. I haven't noticed any big jump on output voltage

Also, you can see PFM operation for few cycles during startup

Could you please confirm status of MODE pin in your circuit

I tried with MODE = VDDA (Single output interleaved operation), following waveform shows the behavior with this configuration

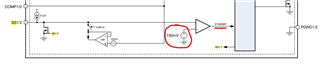

MODE should be tied to AGND if you just want to use only single channel. Sorry I missed this in recommendation.

Hope this answers your questions

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response & solution, im my circuit i tied the MODE to VDDA. After connecting the MODE pin to AGND, smooth raise was observed at 3.3Vout. But if we connect MODE pin to VDDA, why the output raise not follow the ss raise.

Thanks & Regards

Roshan

Hi Roshan

I have talked about it in my previous reply. Device won't take SS reference until SS crosses internal offset. Reference to device would be zero. Slight variation in Vout would cause COMP to go high and thus Vout will rise immediately. This is more prominent in multiphase setup (MODE = VDDA) due internal design. Comp will try to correct it however due to loop delay it increases to significant value. As load current is zero, output won't discharge much and will remain close to increased value.

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response,

I have talked about it in my previous reply. Device won't take SS reference until SS crosses internal offset. Reference to device would be zero. Slight variation in Vout would cause COMP to go high and thus Vout will rise immediately. This is more prominent in multiphase setup (MODE = VDDA) due internal design. Comp will try to correct it however due to loop delay it increases to significant value. As load current is zero, output won't discharge much and will remain close to increased value.

If we configure the converter as interleaved , the converter output will raise smooth as ss raise or it will raise as step.

Thanks & Regards

Roshan

Hi Roshan

In interleaved operation it would rise as step.

Thank you

Regards

Onkar Bhakare

Hi Roshan

Let me know if you have further questions. Kindly close the thread if you feel you query has been resolved.

Thank you

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response, I have another module as interleaved configuration (50vin, 5V@30A). Its output follows w.r.t ss voltage.

But when we use single channel as (MODE = VDDA), by leaving CH2 unused pin as open with tying EN2 to GND and VCCX to GND, FB2 to VDDA. The step raise was observed at output. Also with the same configuration FB2 to external feedback resistor, the output raise was observed w.r.t ss voltage raise.

Thanks & Regards

Roshan

Hi Roshan

Also with the same configuration FB2 to external feedback resistor, the output raise was observed w.r.t ss voltage raise.

Thanks for letting us know your observation. I haven't tried this before

Regards

Onkar Bhakare

Hi Onkar Bhakare,

Thank you for your response,

Thanks for letting us know your observation. I haven't tried this before

May you tell the reason

Thanks & Regards

Roshan

Hi Roshan

I will test this on EVM and get back to you

Thank you

Regards

Onkar Bhakare