Tool/software:

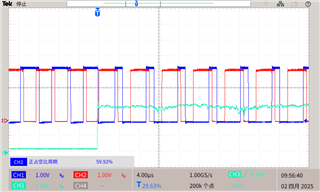

ch1:DPWM0A ch2:DPWM0B ch3:AD03

The opology is BUCK. So the dutu maybe above 50%.The DPWM mode is Multi Mode. The requirement is CBC on DPWM0A only and DPW0B duty cycle matches to DPWM0A. The DPWM Setting is as follow:

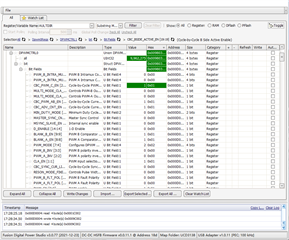

In the datasheet(Page49 table2-5), the mentioned registers have been set. But in the test wave, DPW0B is not match DPWM0A.

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_THRESH = 100;

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_SEL = 0; /* Use threshold register for trip */

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_POL = 1; /* Above thresh to trip */

FaultMuxRegs.DPWM0CLIM.bit.ACOMP_B_EN = 1;

FaultMuxRegs.DPWM1CLIM.bit.ACOMP_B_EN = 1;

Can you help me to see that which register not set? Thank you very much!