Tool/software:

Hello,

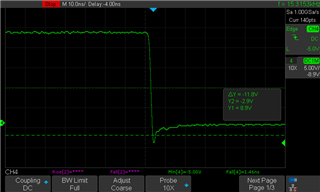

I am currently using the DCDC controller to implement a buck covnerter 24/5V. I am validating the desing and I was taking a look at the overshoots in the switching node to make sure I am not exceeding the maximum aboslute ratings. The rating specfied of the switching node pin in the datasheet is -3V and 33V for 100ns. However in my case I have come accros the following issue:

The turn off overshoot reaches -5V and a base value when on of -500mV and the turn on is not in the image but I have measured about 500mV

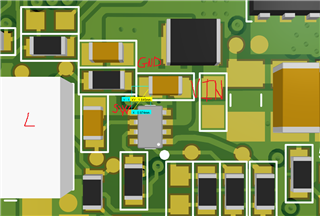

The measure is done by using the oscilloscope Teledyne T3DSO124 of 200MHz BW and 1GSa/s, the probe used is a probe CAT 2 with 200MHz BW. I am measuring the following points as shown in the PCB:

I am measuring using the GND in the closest decoupling input capactior and I am measuring directly in the SW pin. I am wondering why the turn off overshoot is perfect(Around 500mV overshoot and 24V input) but the turn on Overshooot reaches -5V. Furthermore, I though the IC would have already blown regarding that is surpasses quite a lot the recommended operating conditions and I am wondering If you could help me with this issue. I would like to understand where this overshoot comes from and what is done worng in the design, Also, I would like to know if I should except the IC to break soon.

Regards,

David