Tool/software:

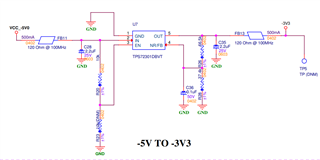

we are using TPS72301DBVT as -5V to -3.3V converter. but we are getting Output ripple more than 100mV. We used all the Input, output capacitors according to Datasheet.

am not able to find the reason.

hope you will resolve my issue, thanks in advance.