Tool/software:

HI,

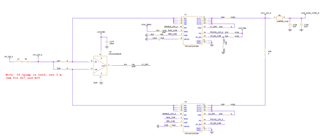

Based on the previous discussion, I have connected two TPS7A5701RTER is parallel as shown below. I am using Opamp just as optional circuit. This part of the circuit is kept DNP.

Request you to review and give feedback. I have some specific queries related to this circuit.

> Whether bias, PGOOD and CP_EN pins can be shorted between two LDO's?

> What is the purpose of Ballast resistor (R34 and R26)? If they are used for sensing current, whether sense pin should be connected after ballast resistor ?

Thanks

Bharati