Tool/software:

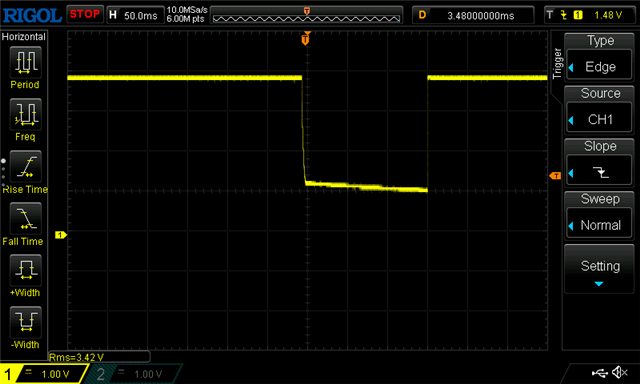

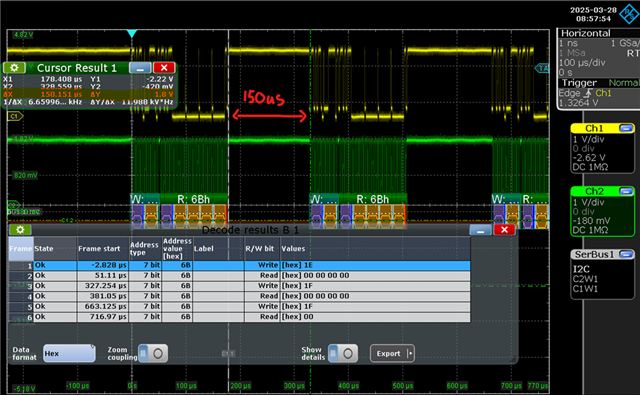

The customer designed the Battery Charger circuit using BQ25622E, . When I2C runs in standard mode (100kHz), there seems to be no problem, But when I2C is running in fast mode (400kHz), the device is not working normally, and they checked that the VSYS output of the BQ25622E dropped to about 1V for about 150us. (See the waveform below). They increased Tbuf to 100us or more as shown in the waveform below, but the symptom continues to occur. Can you please help provide any suggestion that might cause this issue? Thank you!