Tool/software:

Howdy,

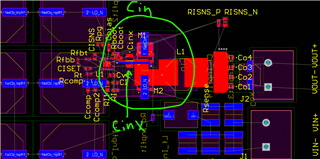

On a previous post I asked some question on the layout of 48V to 5V (17A output) buck converter using the LM5190 chip. Attached is a picture of PCB with some preliminary placements of components, without tracing completed. I once again have questions pertaining to creating a PCB similar to the EVM:

1. The data sheet in 7.4.1.1 mentions that for loop 1 "connect the input capacitor or capacitors negative terminal close to the source of the low-side MOSFET. Similarly, connect the input capacitor or capacitors positive terminal close to the drain of the high-side MOSFET." Since I have a large, beefy input capacitor to connect there, I found that placing it on the bottom side of the PCB would meet those requirements. I attached a picture (but if needed I can send files) to show this: there is one input capacitor to the left of the FETs, and another one at the bottom of the FETs. Is it reasonable to use this configuration? Does tracing loop 1 through the bottom plane cause issues? Might it interfere with the input filter I have placed somewhat near it?

2. I looked at the EVM and I notice there are a lot of vias to place. Is there a script that TI uses to generate all the vias that connect the planes? That would be helpful.

Thanks,

Yoav Binyamin,

Texas A&M University