Tool/software:

Dear Champ,

Customer reviewed TPS6521910RSMR TRM, there are some NVM default settings regarding PMIC ON/OFF control and RESET need further clarifications as followers.

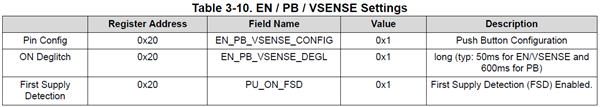

- Pin-25 “EN / PB / VSENSE”

- Why this pin be config to push button as default?

- Any specific applications that AM67x focused need push button for power ON/OFF controlling by manual operation (press and hold 600ms)?

- FSD be enabled as default. Does it mean PMIC will AUTO power ON without long pressing bush button once power valid first time?

- If sudden power loss appeared during power ON procedure, any backup mechanism for fail recovery to prevent PMIC stuck?

- Is it possible to re-program this pin to be EN as default?

- If this pin be config to EN as default, then EN be transient from HIGH to LOW would enable PMIC internal discharge circuit (supposed it had) on each power rails or not?

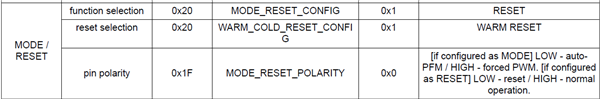

- Pin-28 “MODE / RESET”

- Why this pin be config to WARM reset rather than COLD reset?

- Any side effect once modify this pin to be cold reset as default?

- TPS6521910RSMR NVM write operation or re-programming

- NVM can be re-program multi-times or not?

- Is it possible to modify NVM default setting upon programmed PMIC?

- If we want to partial modify NVM default settings via software command, then this modify or change still be valid or not after power cycling?

BR, Rich