Other Parts Discussed in Thread: TDA4VL, TPS3890-Q1,

Tool/software:

Hi expert,

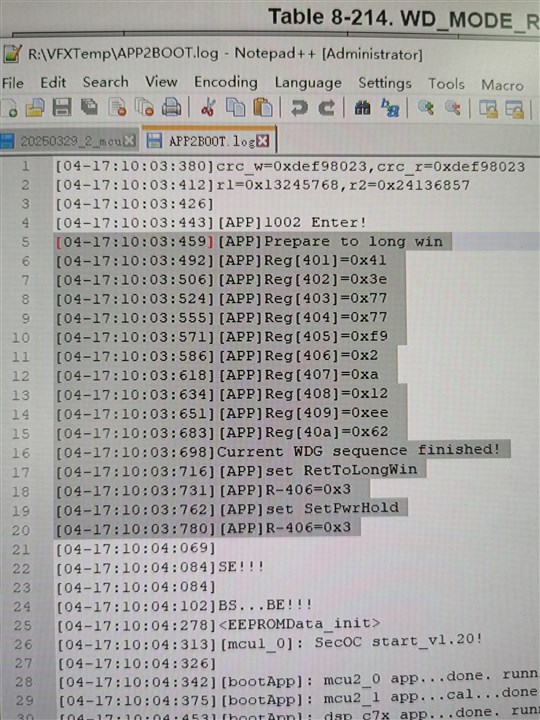

Now I try to integrate TPS6594 WDG driver into TDA4VL SDK,the watchdog will work in Q&A mode.My SDK version is pdk_j721s2_08_05_00_36. The watchdog works normality in MCU1_0.When I need to upgrade software,I have encountered the following problem:

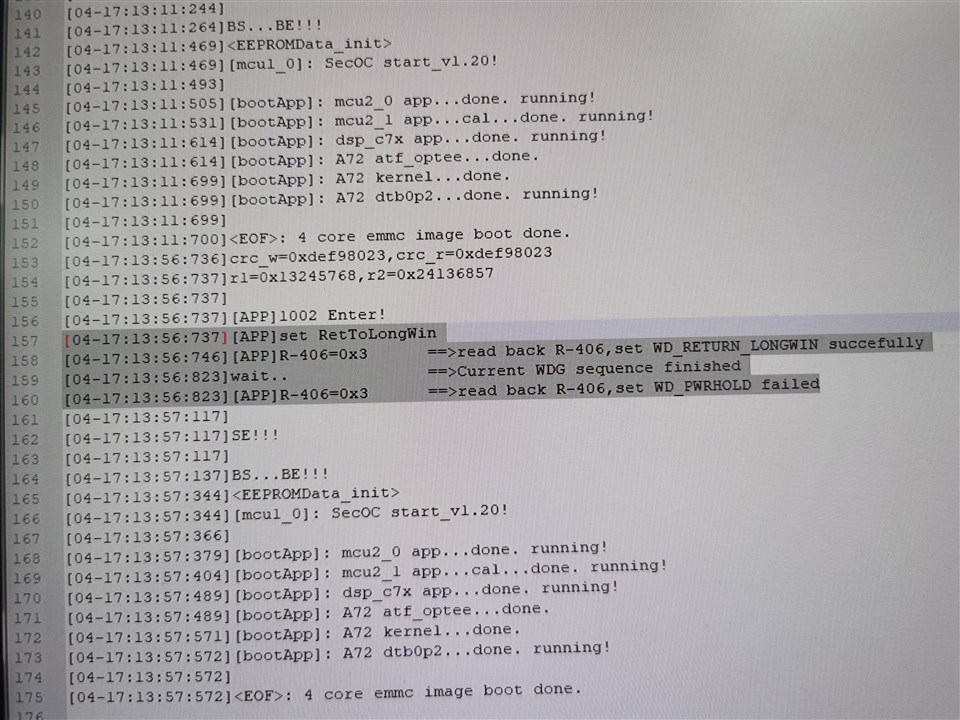

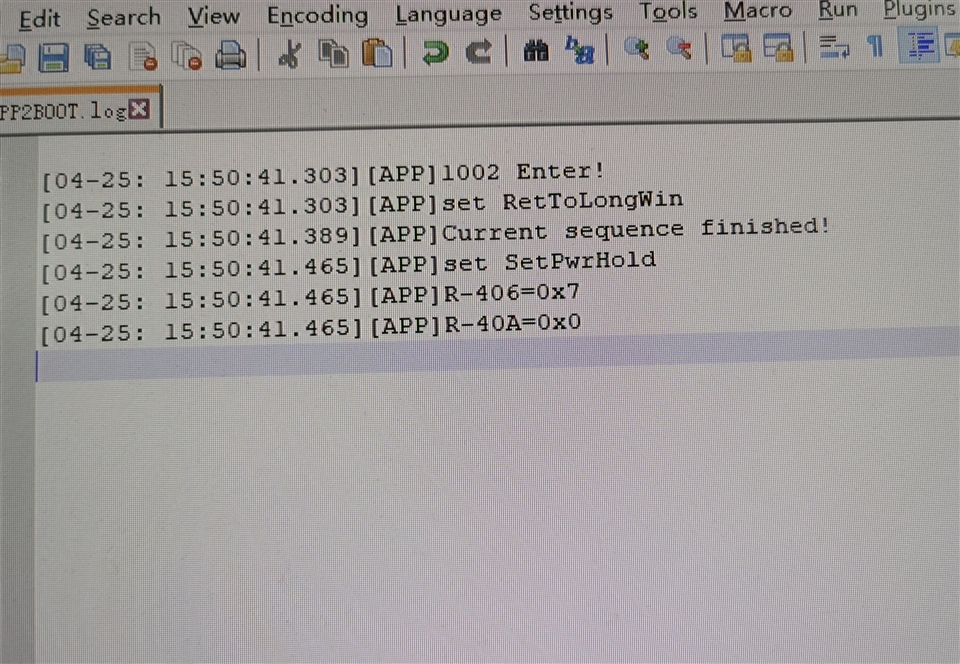

Q1.When received SW upgrade command,the system set WDG return to long window(WD_RETURN_LONGWIN=1),and set it to stay in long window(WD_PWRHOLD=1),but the watchdog just reboot immediately,how can let it stay in long window?

Q2: After called Sciclient_pmDeviceReset(),the system reboot and go into BOOT program,how to resume the watchdog operation?

best regards!

wl.wang