Tool/software:

Hello,

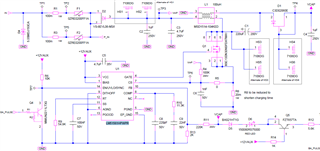

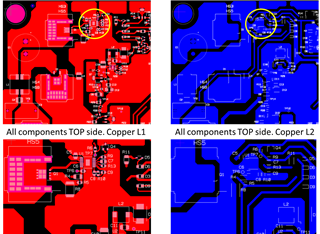

we have implemented a regulator with your component in SEPIC mode to produce an output of 110V, with a wide range input of 16.8V to 137.5 V.

The proto is working, but EMI disturbances are very high, due to LM51561H behavior and its circuitry. We need to lower at 15-20dB to comply to railways standards.