Tool/software:

Hello,

I am evaluating if the LM27762 can be used as a bipolar voltage souce for an ADCs AVDD/AVSS.

The LM27762 is fed by a 3.3 voltage supplly which als feeds the DVDD of the ADC.

Some reference designs and evaluation boards are doing just that:

https://www.ti.com/tool/TIDA-01434

https://www.ti.com/tool/ADS1235EV

When applying a small load of 1 to 10 mA on Vout+/Vout-, I am measuring a ripple with peak to peak of 37 mV on Vin.

When increasing the load, the frequency shifts from 5 kHz to higher kHz until the ripple is "gone" when a load of 80 to 100 mA is applied.

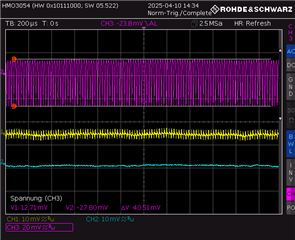

Ch3 : Vin(purple) Ch1 : Vout+(yellow) Ch2: Vout-(cyan)

Load:1 mA Vin:3.3 V Vout+ : 1.81 Vout- : -1.85

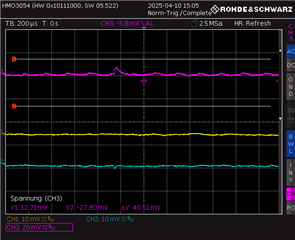

Ch3: Vin; Ch1:Vout +; Ch2: Vout -

Load: 10 mA

no ripple Loard : 90 mA

As you can see, the ripple in Vin is causing a ripple in Vout+ too.

My questions Are:

Can this ripple on Vin be an issue for the DVDD of the adc? Note: I am using the same 3.3 V power supply for LM27762 and the adc DVDD.

Can this ripple have an influence on the measurements taken by the adc? Since The ref. designs above are doing it, my guess is not?

Can the ripple on Vin be reduced?

Regards

Johannes