Other Parts Discussed in Thread: UCC21520

Tool/software:

Hi,

We would like to inquire about the following three technical topics regarding the UCC21551 isolated gate driver:

The UCC21551 is offered at a significantly lower price point compared to other 2-channel reinforced isolation gate drivers from TI (e.g., UCC21520).

We assume that this cost difference may be due to differences in feature set, internal architecture, isolation specifications, or manufacturing process.

Could you please clarify the main technical or design trade-offs that contribute to this lower cost?

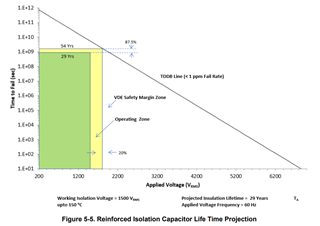

In applications where commercial AC line-related noise (e.g., 50Hz or 60Hz waveform leakage or AC ripple voltage) is continuously coupled to the high-side terminal of the isolated gate driver,

is there any concern regarding long-term reliability, degradation, or abnormal behavior due to stress on the internal isolation barrier or output stage?

Specifically, if such low-frequency AC noise is superimposed across the isolation barrier for extended durations, could this affect insulation lifetime or functional stability?

If any internal evaluations or design guidance exist related to this use case, we would appreciate it if you could share those details.

In a half-bridge configuration, if both high-side and low-side FETs are accidentally turned on simultaneously (i.e., shoot-through condition),

what kind of failure modes are expected within the isolated gate driver?

We are particularly interested in potential damage mechanisms at the output stage, breakdown of internal circuits, or insulation failure under such stress.

Any known failure analysis or test results under this condition would be appreciated.

Best regards,

Conor