Tool/software:

Hi Team,

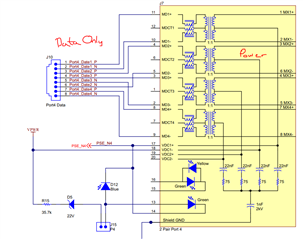

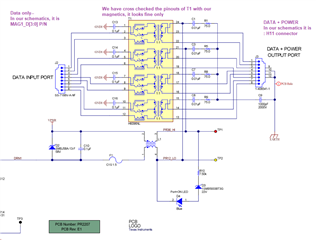

We are using TPS23882B1RTQR in our design for POE section.

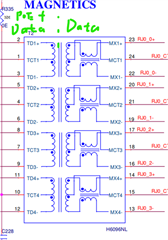

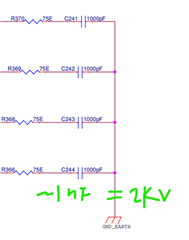

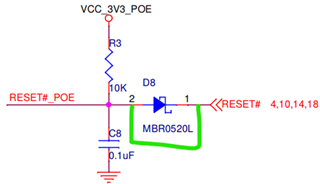

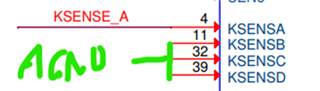

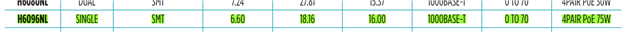

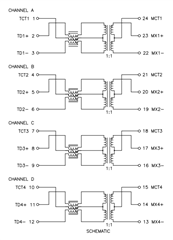

We have referred the TPS23882EVM used guide and designed exactly as per the reference design.

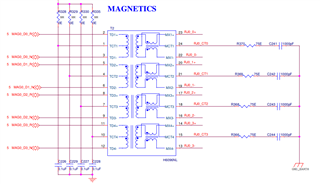

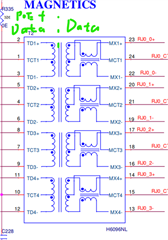

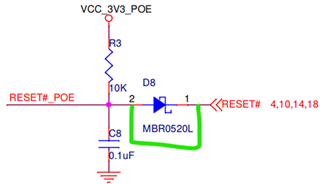

Please find the attached schematics for your reference.

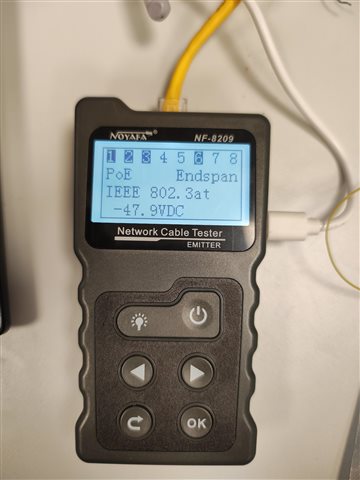

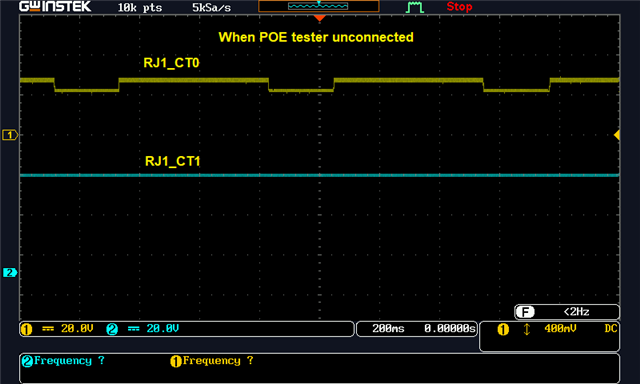

After power ON & connecting 48V, our observations as follows

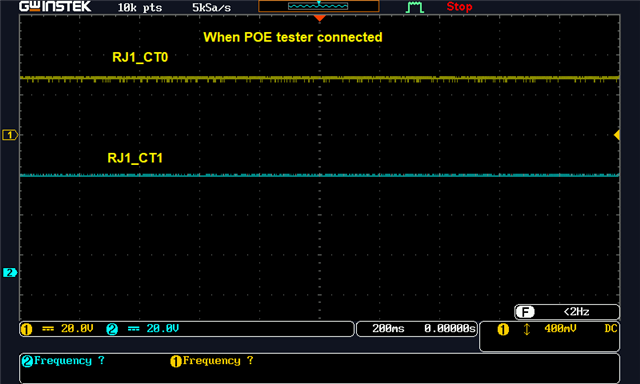

RJ1_CT1 : is 48V, which is OK.

AT RJ1_CT0 : We should get 0V after connecting properly, but we getting 22-27V.

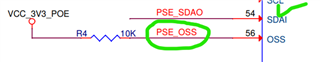

CH2_GATE : 0.4V, CH2_SEN : 0.4V, PSE_N2 is toggling from 22-27V.

Please guide us.

Regards

GuruPDF-EPCB-9038-O-00_texas.pdf