Tool/software:

Hello,

I'm working on a project involving the TPS25751, and I’d appreciate assistance confirming or correcting our approach for patch loading via I²C host controller (STM32).

Setup Overview

-

TPS25751D powered from VBUS (USB PD Source input)

-

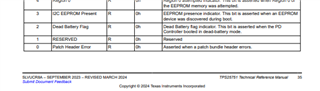

No EEPROM connected

-

Using STM32G070 as I²C host

-

Patch generated using TI Application Customization Tool (exported

.json,.c, and.bin) -

I²C communication confirmed working at address 0x20 (SafeMode)

-

Using target I²C pins for patch delivery (not controller I²C)

-

ADCIN1 = 3.3V (code 7), ADCIN2 = GND (code 0) → SafeMode + I²C address #1

What Works

-

TPS25751 is detected after boot (

Boot Flags = 0x05,Mode = 0x04) -

I²C patch delivery works:

-

Patch array is EEPROM-style: sent from address 0x00 in 16-byte blocks

-

All bytes are transmitted successfully (confirmed via debug print)

-

-

Read registers after patch load:

-

Boot Flags = 0x05 -

Mode = 0x04 -

But never enters

Boot Flags = 0x07(APP mode)

-

What’s Not Working

-

TPS never jumps to APP mode even after full patch load (0x1E00 bytes)

-

Tried multiple patch formats: full flash (

.c,.bin), low region only, known-good test arrays -

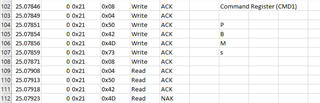

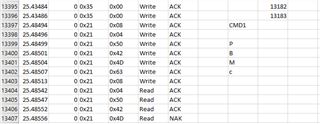

Implemented PBMs protocol:

-

Wrote 7-byte bundle descriptor to

DATAxregisters -

Wrote

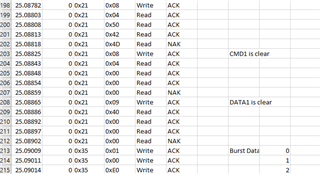

CMD1 = 0x01to initiate PBMs -

TPS responds with

CMD1 = 0x04consistently (command rejected) -

DATA1always shows error (not 0x00)

-

-

Verified that:

-

I²C address = 0x20

-

Patch size is correct (7680 bytes)

-

Timeout is reasonable (0x20 = 3.2s)

-

Could you please confirm the correct procedure to load a patch via I²C host in SafeMode for the TPS25751?

Specifically:

-

Is there an official

.binor.cexport format that is guaranteed to be I²C-host loadable, with APP jump entry? -

Is PBMs required, or is EEPROM-style I²C load from

0x00sufficient in SafeMode? -

What exactly does

CMD1 = 0x04indicate during PBMs? -

Can you provide a minimal

.binor.cpatch bundle for SafeMode testing that is verified to reachBoot Flags = 0x07via I²C?

We would like to load the patch from STM32 on every power-up, without needing external EEPROM. Your help confirming the steps (or providing a known-good patch) would be greatly appreciated.

Thank you for your time and support,

Regards,

Sergey