Tool/software:

Hello,

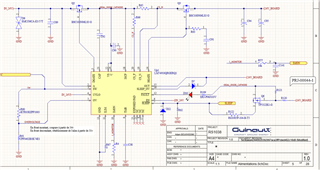

I am using the LM74910 in the following design, the goal is to disable the sleep mode at startup in order to charge the 6.6 mF capacitors and then, when the 24V_BOARD reaches IN_24V - Vgs_th, the sleep pin goes to 0v.

This allows to charge the capacitors and go to sleep mode right after that.

The problem with this design is that, in case of OCP when the sleep mode is disabled, something goes wrong with the LM74910 and it never shuts off the HGATE again, even when it's in sleep mode - OCP - OVP.

Any ideas why the IC fails with this design ?

THanks !