Tool/software:

Hi,

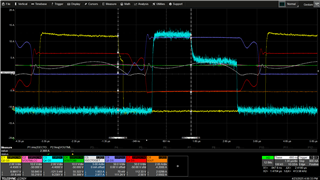

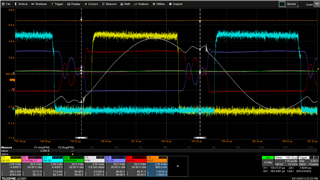

We have an LLC converter with center-tapped secondary output. We are using UCC24612-2 for SR application on both output FETs. One of the FETs is generally seeing longer "Forced Proportional Gate Drive". The layout for both FETs are pretty similar. Please see waveform below:

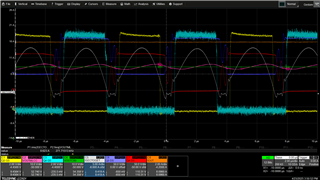

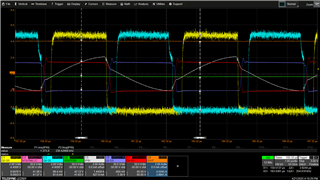

Even at near resonance, we see a similar behavior but difference is less stark

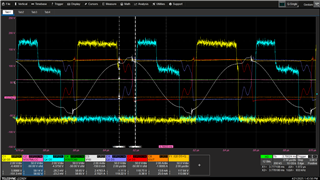

Below resonance, similar:

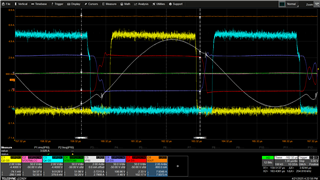

Above resonance, similar:

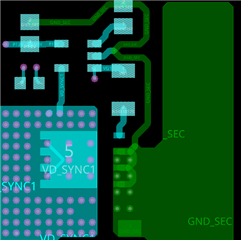

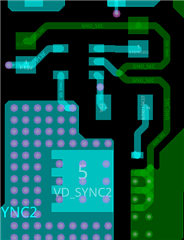

Layout Snips for both FETs:

Q5:

Q4:

Can you suggest what might cause this? And could it be dangerous in any corner case?