Tool/software:

Hi,

We are using UCC21755 gate drivers for driving SiC mosfet. I wanted to know about the active pull down feature on this isolated gate driver.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

We are using UCC21755 gate drivers for driving SiC mosfet. I wanted to know about the active pull down feature on this isolated gate driver.

Yes, active pull down keeps the OUT pins clamped to VEE (even when VDD is open/not powered),

Based on the description,

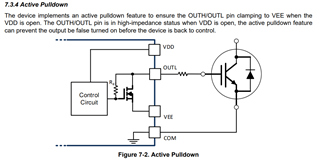

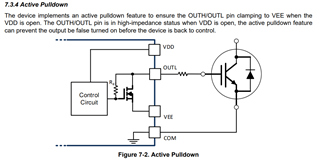

The device implements an active pulldown feature to ensure the OUTH/OUTL pin clamping to VEE when the VDD is open. The OUTH/OUTL pin is in high-impedance status when VDD is open, the active pulldown feature can prevent the output be false turned on before the device is back to control.

Thanks

Sasi