Other Parts Discussed in Thread: TMS320F28377D

Tool/software:

Hi TI Team,

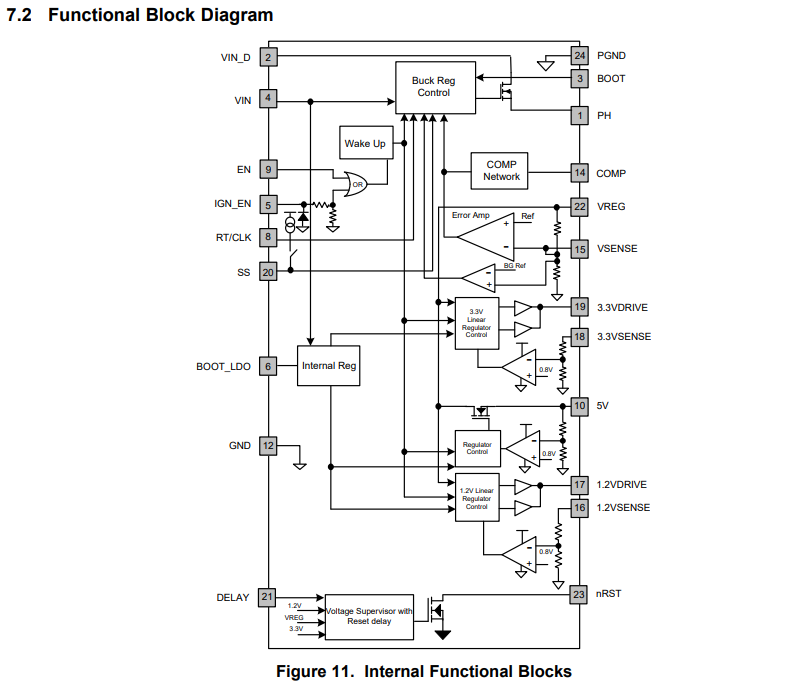

I’m working on implementing a redundant power supply architecture using the TPS65300-Q1 PMIC, which I intend to activate only in the event of a failure in my primary power supply (a set of buck converters providing 1.2V, 3.3V, and 5V).

Use Case Summary:

- The primary rails (1.2V, 3.3V, 5V) are generated by discrete buck converters.

- These rails power a C2000 microcontroller (TMS320F28377D) and supporting peripherals.

- I have the option to place diodes at the output of the buck converters, and the plan is to use the PWRGOOD signal of each buck to monitor failures.

- In case of failure, I’ll use the PWRGOOD signal to control the EN pin of the TPS65300-Q1, enabling the backup supply.

- The diode ORing is done only at the output of the bucks — I have not placed diodes at the output of TPS65300-Q1, primarily to avoid voltage drops that I can’t easily compensate with feedback or margining.

Questions:

- Behavior of VSENSE Pins Before EN = High:

Since the TPS65300-Q1 isn’t enabled under normal operation, but the system’s 1.2V and 3.3V rails are already live from the primary supply, will applying voltage to the 1.2VSENSE and 3.3VSENSE pins before EN is asserted cause any issues?- Will this lead the device to erroneously detect a fault or go into a fault state, possibly delaying or blocking turn-on when the EN pin is eventually pulled high?

- Will this lead the device to erroneously detect a fault or go into a fault state, possibly delaying or blocking turn-on when the EN pin is eventually pulled high?

- Does the IC assert any signal or condition based on VSENSE when EN is low?

I’m wondering if the PMIC might try to act on or monitor the VSENSE pins even before it's actually enabled. Does the device assert low (sink current or pull-down) on VSENSE pins when EN is low?

This could break the power ORing behavior or cause unexpected power-up delays. - If needed, can I use a similar diode + feedback compensation strategy as I would with a buck converter—i.e., put a diode at the output and adjust the internal feedback to regulate post-diode? I realize this is non-trivial for PMICs and may not be supported if I connect the VSense pin after the diode.

Would appreciate your insight on this strategy and any advice or application note reference if available.

Best Regard,

Dhaval Ravat

Attachment: https://drive.google.com/file/d/1SAC5Xq6n-QrIDkEZTa7144KCtbl2y6Ja/view?usp=sharing