Tool/software:

Hi Team,

We're using the TPS2373-4RGW Poe PD controller in our design. The hardware has been assembled and is currently under testing.

We've noticed an intermittent issue in some units: the Power Good (PG) output remains low, even though VDD is active — indicating that PoE negotiation has completed successfully and the internal hotswap MOSFET has turned on. This behaviour is inconsistent, showing up roughly once in every 10 power cycles (Hot plugging the LAN cable). We're using the POE300 1.0 as the PSE during testing.

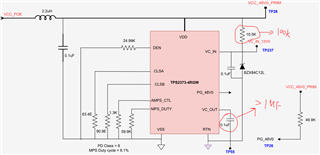

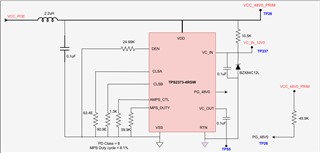

Attaching the image of the design section of TPS2373-4RGW.

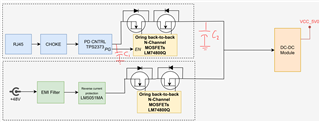

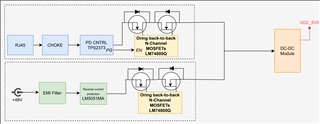

The block diagram of the power section.

Observation:

Please let us know what could be the potential cause of these events.