Other Parts Discussed in Thread: TPS65981,

Tool/software:

Hi TIer

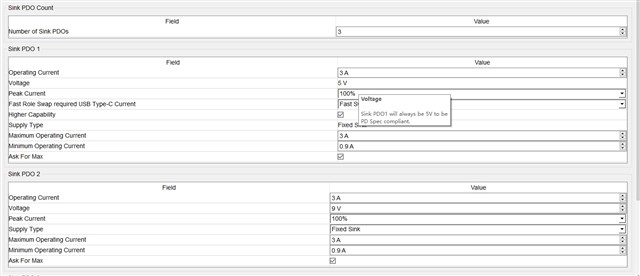

My customer use GUI TPS65981_2_6_7_8 Application Customization 6.1.4 to configure the TPS65987DDH.

When configuring SINK, Customer set the overcurrent protection point to a maximum of 3A, but the actual test found that the PD adapter protection did not shut down the PP channel.

When configuring SOURCE, customer set the external maximum output current to 0.9A, CC pull down 5.1KΩ test and found that the actual test was still us the DCDC 3A overcurrent protection, The PP channel is also not closed.

So could you help to provide some test methods or possible reasons why the OCP settings do not work, whether in source or sink mode.

Thank you very much.